# EMBEDDED SYSTEMS

A CONTEMPORARY DESIGN TOOL

JAMES K. PECKOL

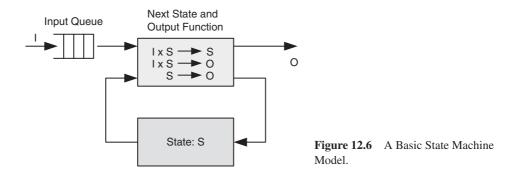

**Embedded Systems**

# **Embedded Systems** A Contemporary Design Tool

**Second Edition**

James K. Peckol, Ph.D.

University of Washington

# WILEY

This edition first published 2019 © 2019 John Wiley & Sons Ltd

*Edition History* 1<sup>st</sup> Edition: Embedded system: a contemporary design tool / James K. Peckol. ISBN 978-0-471-72180-2 (cloth)

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by law. Advice on how to obtain permission to reuse material from this title is available at http://www.wiley.com/go/permissions.

The right of James K. Peckol to be identified as the author of this work has been asserted in accordance with law.

#### Registered Offices

John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, USA John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

#### Editorial Office

The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

For details of our global editorial offices, customer services, and more information about Wiley products visit us at www.wiley.com.

Wiley also publishes its books in a variety of electronic formats and by print-on-demand. Some content that appears in standard print versions of this book may not be available in other formats.

#### Limit of Liability/Disclaimer of Warranty

While the publisher and authors have used their best efforts in preparing this work, they make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives, written sales materials or promotional statements for this work. The fact that an organization, website, or product is referred to in this work as a citation and/or potential source of further information does not mean that the publisher and authors endorse the information or services the organization, website, or product may provide or recommendations it may make. This work is sold with the understanding that the publisher is not engaged in rendering professional services. The advice and strategies contained herein may not be suitable for your situation. You should consult with a specialist where appropriate. Further, readers should be aware that websites listed in this work may have changed or disappeared between when this work was written and when it is read. Neither the publisher nor authors shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

#### Library of Congress Cataloging-in-Publication Data

Names: Peckol, James K., author.

- Title: Embedded systems : A Contemporary Design Tool / James K. Peckol, Ph.D., University of Washington.

- Description: 2nd edition. | Hoboken, NJ : John Wiley & Sons, Inc., 2019. | Includes bibliographical references and index. |

- Identifiers: LCCN 2018039258 (print) | LCCN 2018045459 (ebook) | ISBN

- 9781119457497 (Adobe PDF) | ISBN 9781119457558 (ePub) | ISBN 9781119457503 (hardcover)

- Subjects: LCSH: Embedded computer systems. | Object-oriented methods (Computer science)

Classification: LCC TK7895.E42 (ebook) | LCC TK7895.E42 P43 2019 (print) | DDC 006.2/2-dc23

LC record available at https://lccn.loc.gov/2018039258

Cover Design: Wiley Cover Image: © HYWARDS/iStock.com/Getty Images Plus

Set in 10/12 TimesLTStd by SPi Global, Chennai, India

Printed and bound by CPI Group (UK) Ltd, Croydon, CR0 4YY

10 9 8 7 6 5 4 3 2 1

To my family: Near and Extended, Close and Distant, Present and Departed, So Similar, So Different, So Known, So Surprising ... especially to our youngest brother Karl, taken from us out of season during the last voyage of the Edmund Fitzgerald.

| About the Author            | xxxiii |

|-----------------------------|--------|

| Foreword                    | XXXV   |

| Preface                     | xlix   |

| Acknowledgment              | lix    |

| About the Companion Website | lxi    |

## Part 1 Hardware and Software Infrastructure

| 1 Th | The Hardware Side – Part 1: An Introduction |              |                              |    |  |

|------|---------------------------------------------|--------------|------------------------------|----|--|

| 1.1  | Introdu                                     | Introduction |                              |    |  |

| 1.2  | The Ha                                      | ardware Sic  | le – Getting Started         | 1  |  |

| 1.3  |                                             | ore Level    | 6                            | 3  |  |

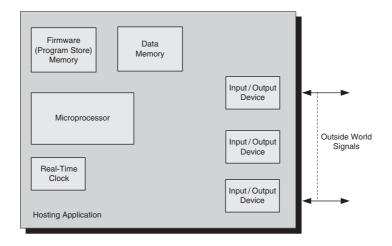

|      | 1.3.1                                       | The Mic      | roprocessor                  | 6  |  |

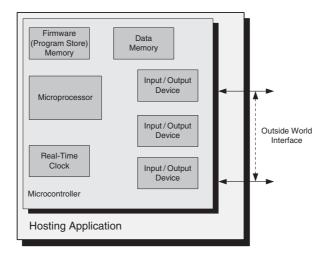

|      | 1.3.2                                       |              | rocomputer                   | 7  |  |

|      | 1.3.3                                       | The Mic      | rocontroller                 | 7  |  |

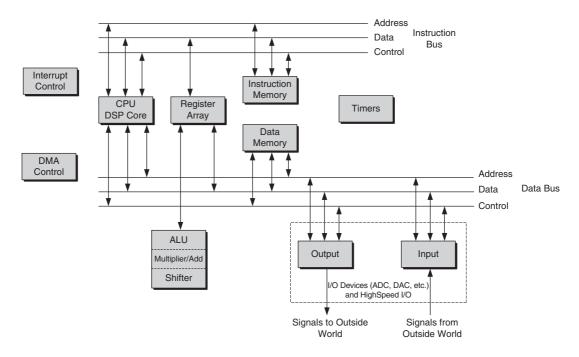

|      | 1.3.4                                       | The Dig      | ital Signal Processor        | 7  |  |

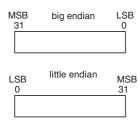

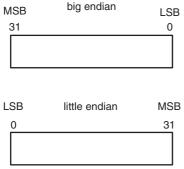

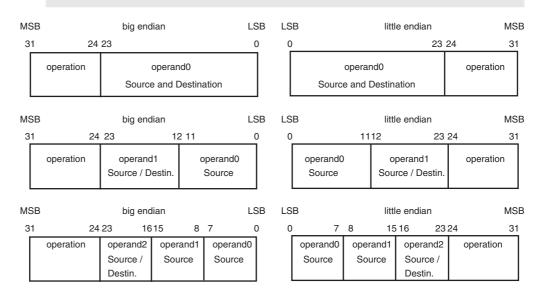

| 1.4  | Repres                                      | enting Info  | -                            | 8  |  |

|      | 1.4.1                                       | Word Si      | ze                           | 9  |  |

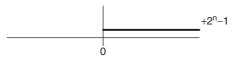

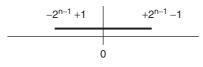

| 1.5  | Unders                                      | standing Nu  | umbers                       | 9  |  |

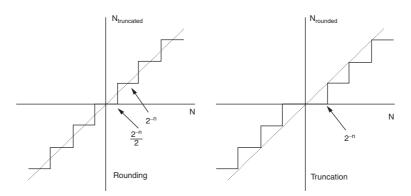

|      | 1.5.1                                       | Resoluti     | on                           | 10 |  |

|      | 1.5.2                                       | Propaga      | tion of Error                | 11 |  |

|      |                                             | 1.5.2.1      | Addition                     | 11 |  |

|      |                                             | 1.5.2.2      | Multiplication               | 12 |  |

| 1.6  | Addres                                      | sses         |                              | 13 |  |

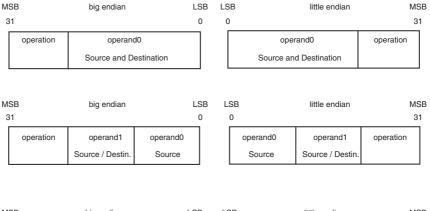

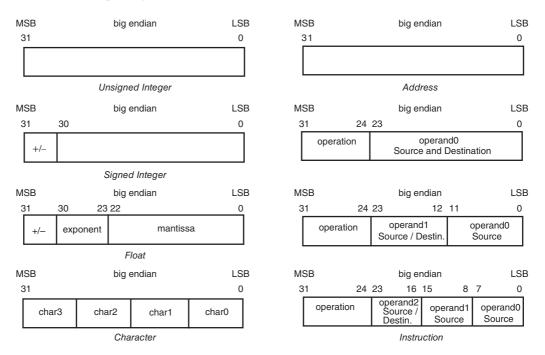

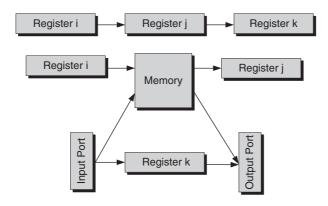

| 1.7  | Instruc                                     | tions        |                              | 14 |  |

| 1.8  | Registe                                     | ers – A Firs | st Look                      | 16 |  |

| 1.9  | Embed                                       | ded System   | ns – An Instruction Set View | 18 |  |

|      | 1.9.1                                       | Instructi    | on Set – Instruction Types   | 18 |  |

|      | 1.9.2                                       | Data Tra     | insfer Instructions          | 18 |  |

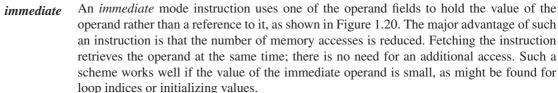

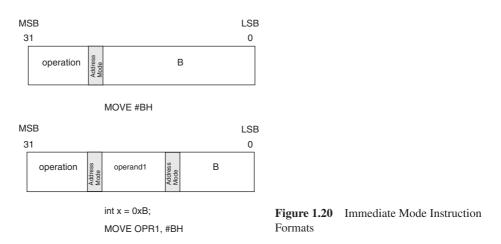

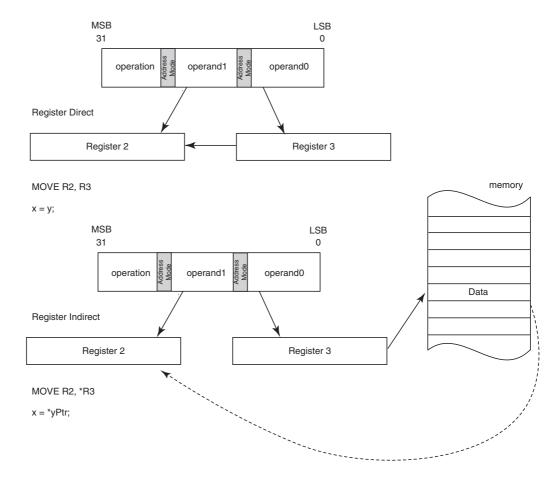

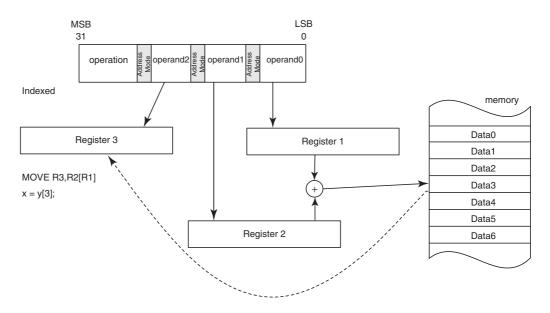

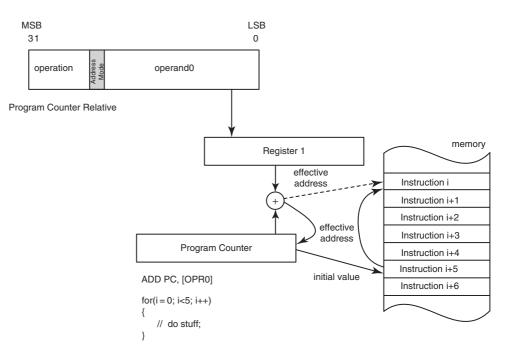

|      |                                             | 1.9.2.1      | Addressing Modes             | 20 |  |

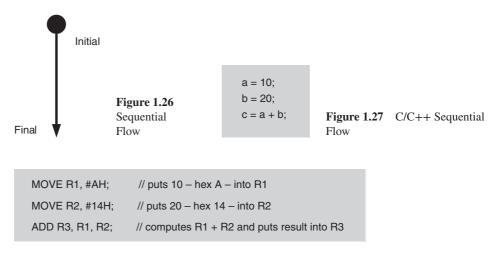

|      | 1.9.3                                       | Executio     | on Flow                      | 26 |  |

|      |                                             | 1.9.3.1      | Sequential Flow              | 26 |  |

|      |                                             | 1.9.3.2      | Branch                       | 27 |  |

|      |                                             | 1.9.3.3      | If-else Construct            | 28 |  |

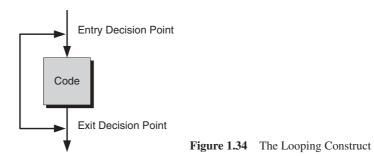

|      |                                             | 1.9.3.4      | Loop                         | 28 |  |

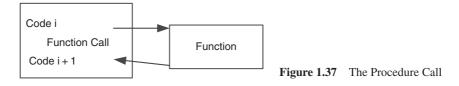

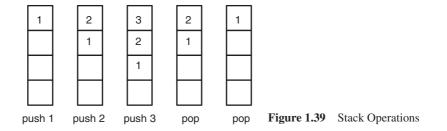

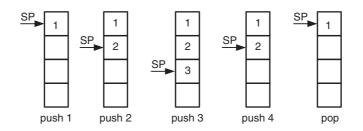

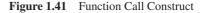

|      |                                             | 1.9.3.5      | Procedure or Function Call   | 29 |  |

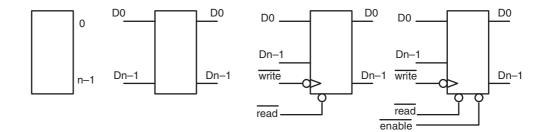

|      |                                             | 1.9.3.6      | Arithmetic and Logic         | 32 |  |

| 1.1  | 0 Embed                                     | ded System   | ns – A Register View         | 34 |  |

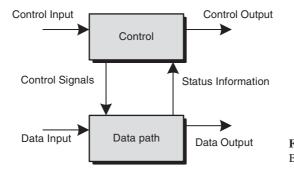

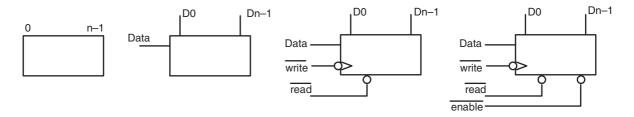

|      | 1.10.1                                      | The Bas      | ic Register                  | 35 |  |

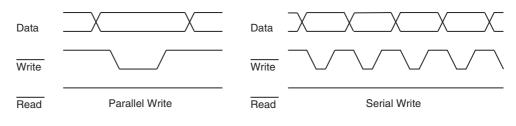

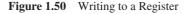

|   |       | 1.10.2       | Register (   | Operations                                       | 35 |

|---|-------|--------------|--------------|--------------------------------------------------|----|

|   |       |              |              | Write to a Register                              | 36 |

|   |       |              | 1.10.2.2     | Read from a Register                             | 36 |

|   | 1.11  | Registe      | r Transfer L | -                                                | 36 |

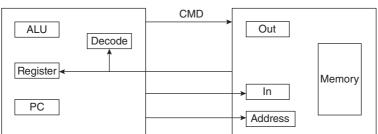

|   | 1.12  |              |              | Microprocessor                                   | 38 |

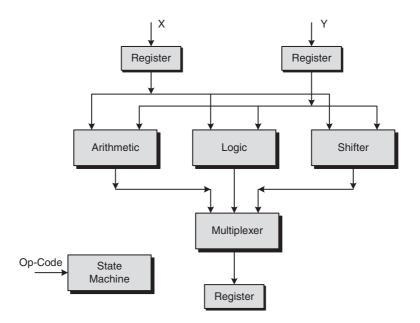

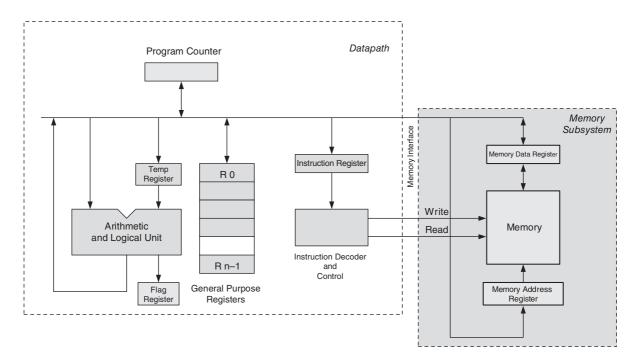

|   |       | 1.12.1       |              |                                                  | 38 |

|   |       | 1.12.2       | Processor    |                                                  | 39 |

|   |       |              | 1.12.2.1     | Fetch                                            | 39 |

|   |       |              | 1.12.2.2     | Decode                                           | 40 |

|   |       |              | 1.12.2.3     | Execute                                          | 40 |

|   |       |              | 1.12.2.4     | Next                                             | 41 |

|   | 1.13  | Summa        | ıry          |                                                  | 45 |

|   | 1.14  | Review       | Questions    |                                                  | 45 |

|   | 1.15  | Though       | nt Questions |                                                  | 46 |

|   | 1.16  | Probler      | ns           |                                                  | 47 |

|   |       |              |              |                                                  |    |

| 2 | The H | ardware      | Side – Part  | 2: Combinational Logic – A Practical View        | 55 |

|   | 2.1   | Introdu      | ction        |                                                  | 55 |

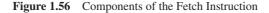

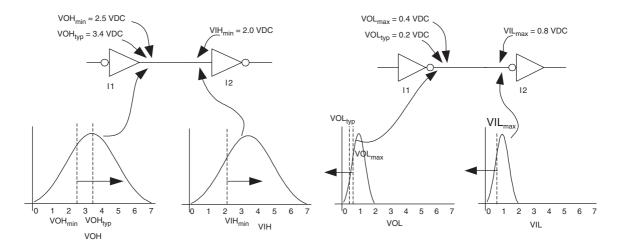

|   | 2.2   | A Look       | at Real-Wo   | orld Gates – Part 1: Signal Levels               | 56 |

|   |       | 2.2.1        | Logic Lev    | vels                                             | 57 |

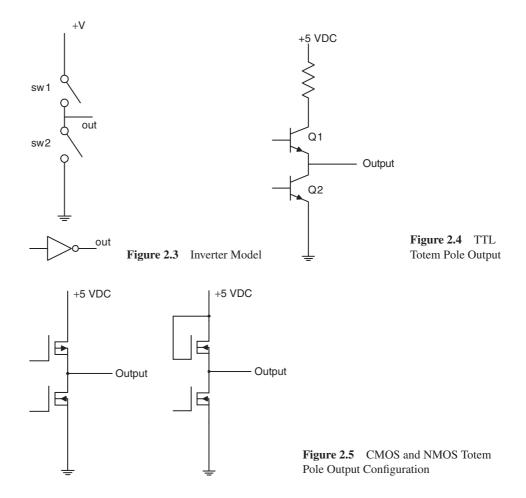

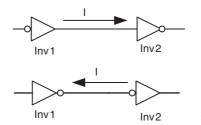

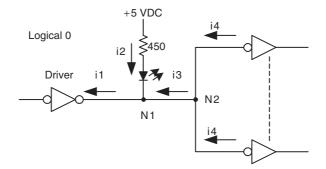

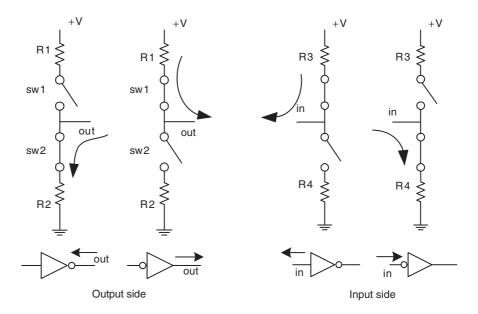

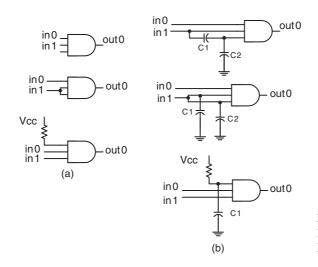

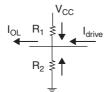

|   |       | 2.2.2        | A First Lo   | ook Inside the Logic Gate                        | 59 |

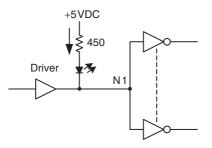

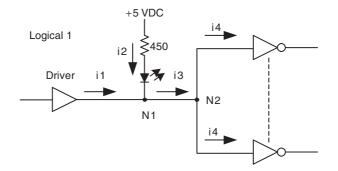

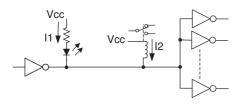

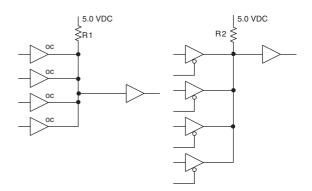

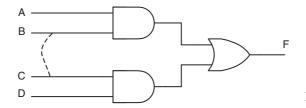

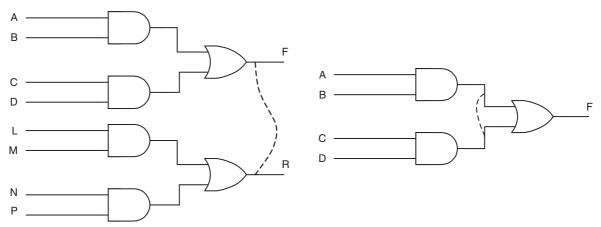

|   |       | 2.2.3        | Fan-In and   | d Fan-Out                                        | 60 |

|   | 2.3   | A Look       | at Real-Wo   | orld Gates – Part 2: Time                        | 64 |

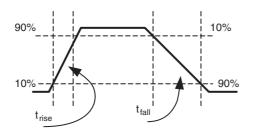

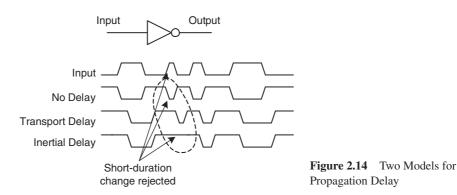

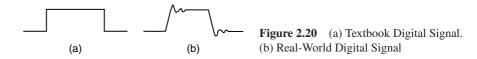

|   |       | 2.3.1        | Rise and I   | Fall Times                                       | 65 |

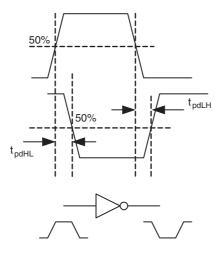

|   |       | 2.3.2        | 10           |                                                  | 65 |

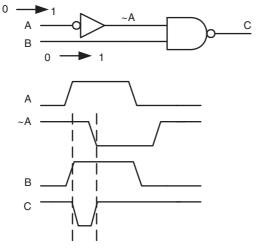

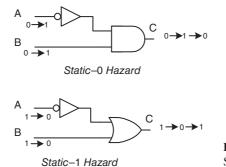

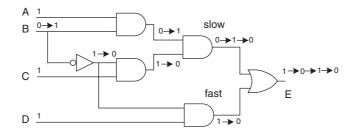

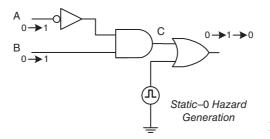

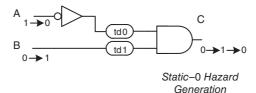

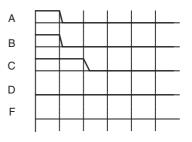

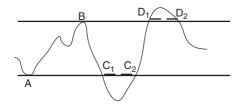

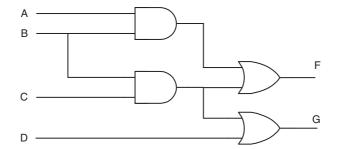

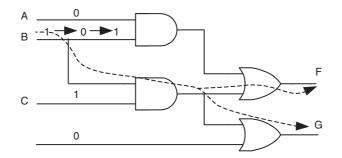

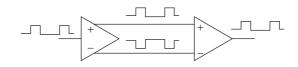

|   |       | 2.3.3        | Race Con     | ditions and Hazards                              | 67 |

|   |       |              | 2.3.3.1      |                                                  | 67 |

|   |       |              |              | Dynamic Hazard                                   | 69 |

|   | 2.4   |              |              | orld Gates – Part 3: Signal Behavior in the Real |    |

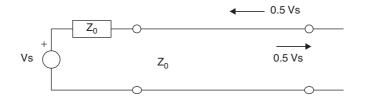

|   |       |              |              | of Early Physicists                              | 70 |

|   | 2.5   |              |              | y – A First Look at Signal Quality               | 71 |

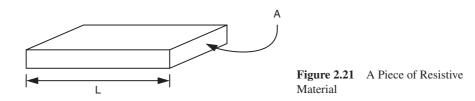

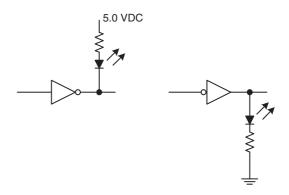

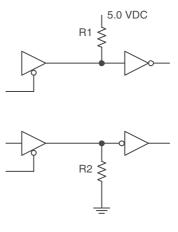

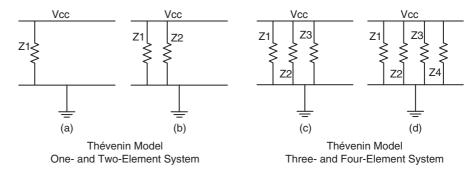

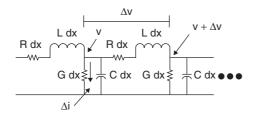

|   |       | 2.5.1        | Resistors    |                                                  | 71 |

|   |       |              | 2.5.1.1      | A Discrete Component First-Order Resistor        |    |

|   |       |              | ~ .          | Model                                            | 72 |

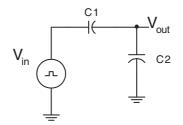

|   |       | 2.5.2        | Capacitor    |                                                  | 74 |

|   |       |              | 2.5.2.1      | Discrete Component First-Order Capacitor         |    |

|   |       |              | <b>x 1</b>   | Model                                            | 76 |

|   |       | 2.5.3        | Inductors    |                                                  | 78 |

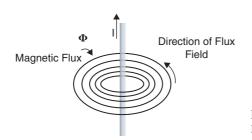

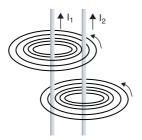

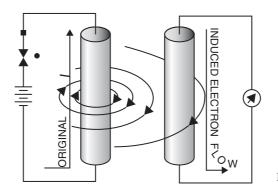

|   |       |              | 2.5.3.1      | Magnetic Field Lines – The First Principle       | 78 |

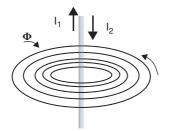

|   |       |              | 2.5.3.2      | Magnetic Field Lines – The Second Principle      | 79 |

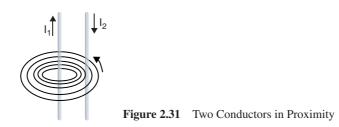

|   | 2.6   | <b>T</b> 1 . | 2.5.3.3      | Magnetic Field Lines – The Third Principle       | 80 |

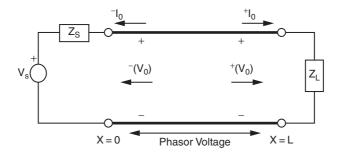

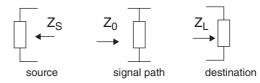

|   | 2.6   |              | nce in Actio |                                                  | 81 |

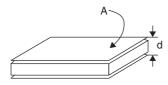

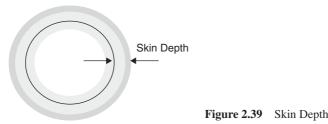

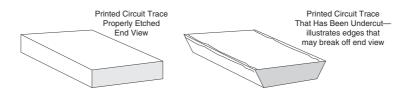

|   |       | 2.6.1        |              | Conductors                                       | 82 |

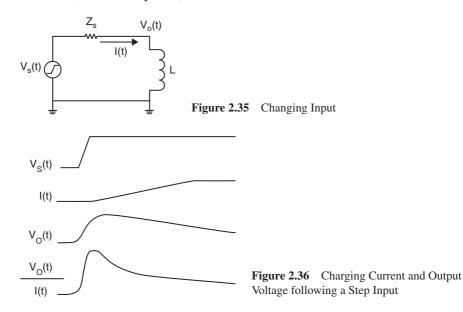

|   | 2.7   | 0            |              | els and Parasitic Components                     | 84 |

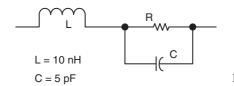

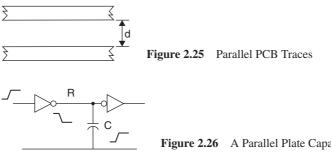

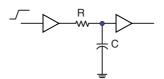

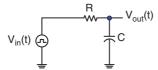

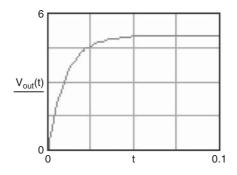

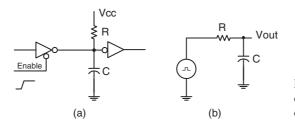

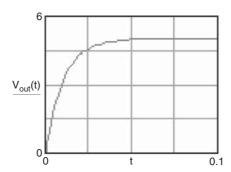

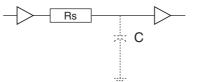

|   |       | 2.7.1        |              | er RC Circuit Model                              | 84 |

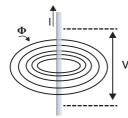

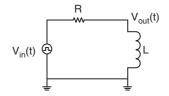

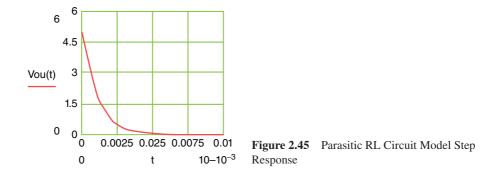

|   |       | 2.7.2        |              | er RL Circuit Model                              | 86 |

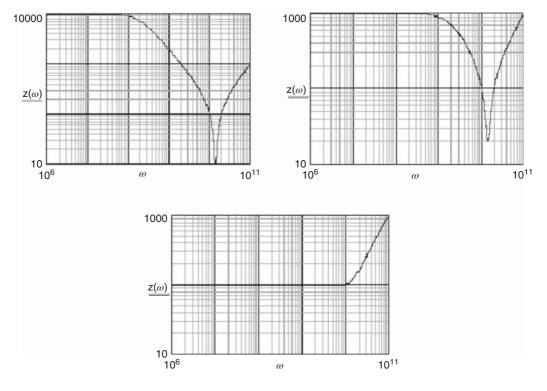

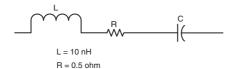

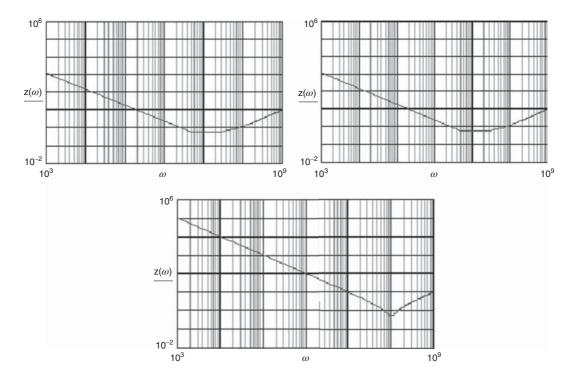

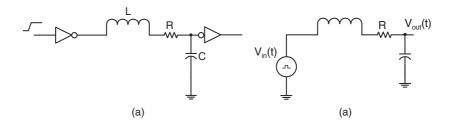

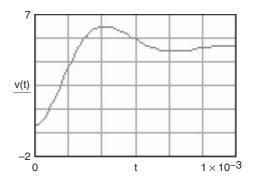

|   |       | 2.7.3        |              | rder Series RLC Circuit Model                    | 87 |

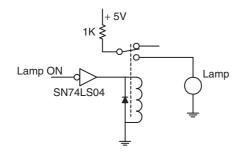

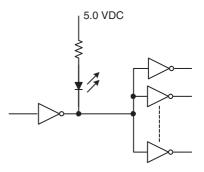

|   |       | 2.7.4        | Tristate D   | rivers                                           | 89 |

|      |          | 2.7.4.1     | Open Gate Inputs                            | 90  |

|------|----------|-------------|---------------------------------------------|-----|

| 2.8  | Testing  | Combinatio  | onal Circuits – Introduction and Philosophy | 91  |

| 2.9  | Modeli   | ng, Simulat | ion, and Tools                              | 92  |

| 2.10 | Structur | ral Faults  |                                             | 93  |

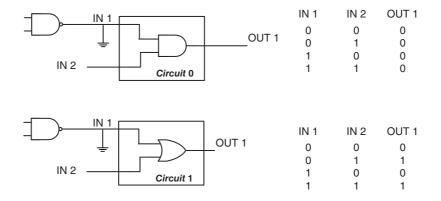

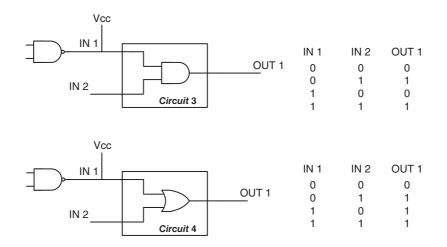

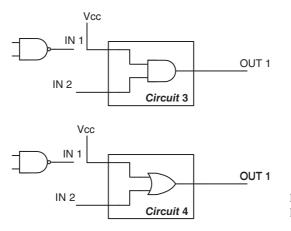

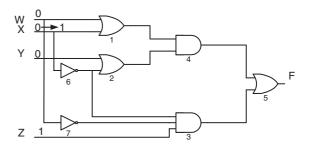

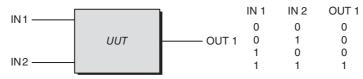

|      | 2.10.1   | Stuck-at H  | Faults                                      | 93  |

|      |          | 2.10.1.1    | Stuck-at-Zero Faults                        | 94  |

|      |          | 2.10.1.2    | Stuck-at-One Faults                         | 95  |

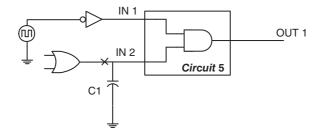

|      | 2.10.2   | Open Cire   | cuit Faults                                 | 96  |

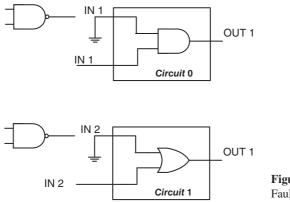

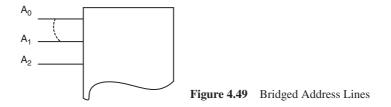

|      | 2.10.3   | Bridging    | Faults                                      | 96  |

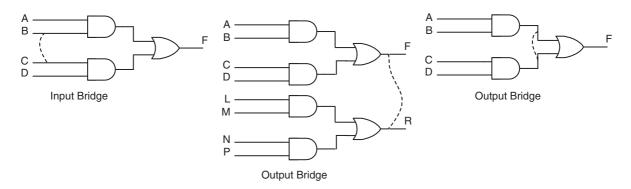

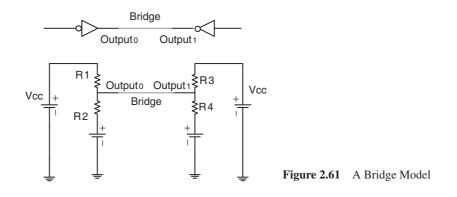

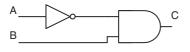

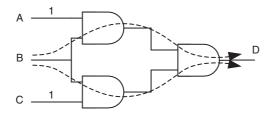

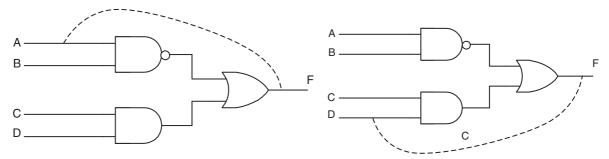

|      |          | 2.10.3.1    | Nonfeedback Bridge Faults                   | 97  |

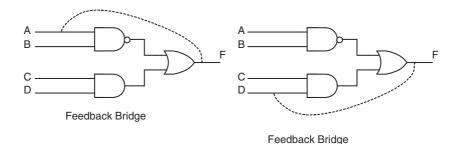

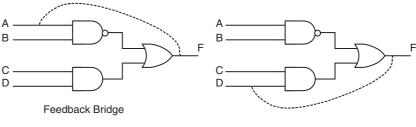

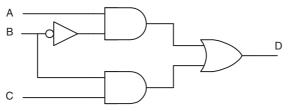

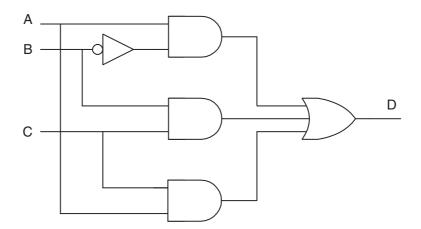

|      |          | 2.10.3.2    | Feedback Bridge Faults                      | 99  |

| 2.11 | Functio  | nal Faults  |                                             | 99  |

|      | 2.11.1   | Hazards a   | nd Race Conditions                          | 100 |

| 2.12 | Summa    | ry          |                                             | 101 |

| 2.13 | Review   | Questions   |                                             | 101 |

| 2.14 | Though   | t Questions |                                             | 102 |

| 2.15 | Problem  | ns          |                                             | 104 |

|      |          |             |                                             |     |

### 3 The Hardware Side – Part 3: Storage Elements and Finite-State Machines – A Practical View

| 1 | 1 | 1 |

|---|---|---|

|   |   |   |

| 3.1 | Introdu | iction       |                                                   | 111 |

|-----|---------|--------------|---------------------------------------------------|-----|

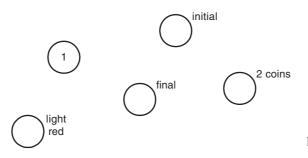

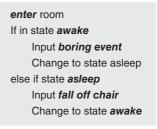

| 3.2 | The Co  | oncepts of S | tate and Time                                     | 112 |

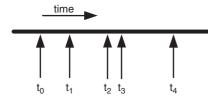

|     | 3.2.1   | Time         |                                                   | 112 |

|     | 3.2.2   | State        |                                                   | 112 |

|     | 3.2.3   | State Cha    | anges                                             | 113 |

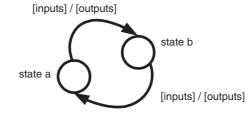

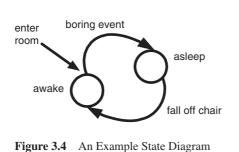

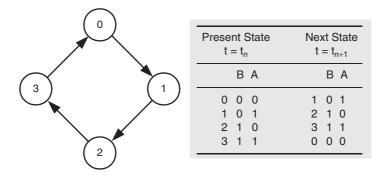

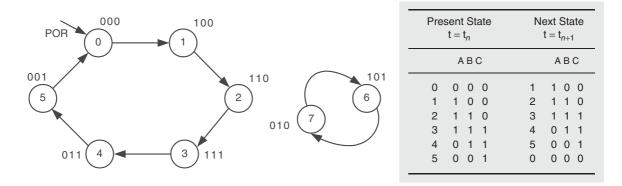

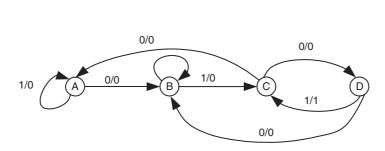

| 3.3 | The Sta | ate Diagran  |                                                   | 113 |

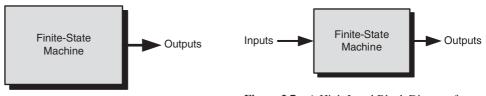

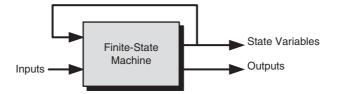

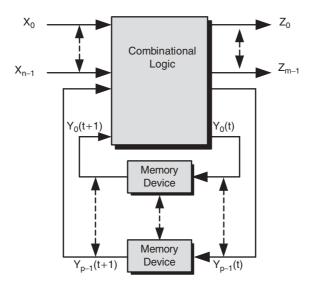

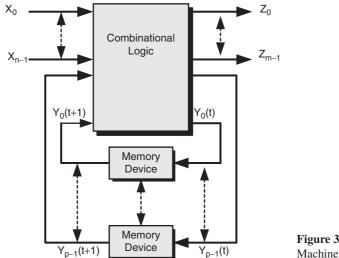

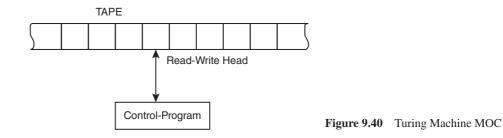

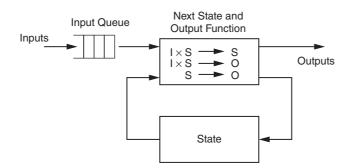

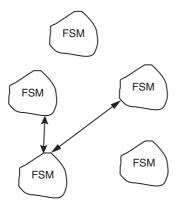

| 3.4 |         |              | ines – A Theoretical Model                        | 114 |

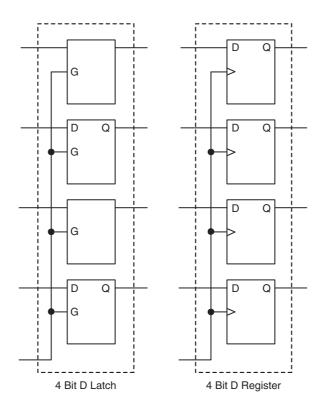

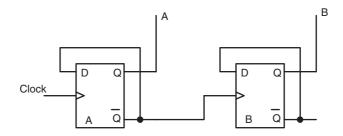

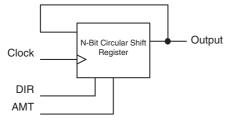

| 3.5 | Design  | ing Finite-  | State Machines – Part 1: Registers                | 116 |

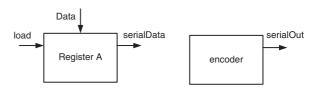

|     | 3.5.1   | Storage I    | Registers                                         | 116 |

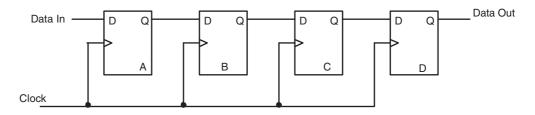

|     | 3.5.2   | Shift Reg    | gisters                                           | 117 |

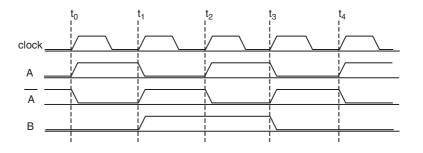

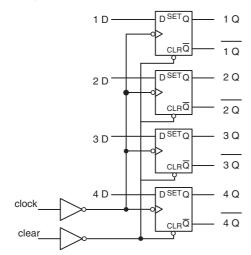

|     |         | 3.5.2.1      | Shift Right Shift Register                        | 117 |

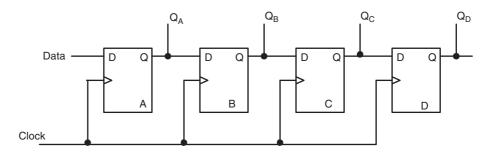

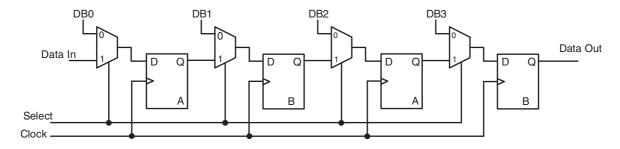

|     |         | 3.5.2.2      | Parallel In/Serial Out – Serial In/Parallel Out   |     |

|     |         |              | Left Shift Registers                              | 121 |

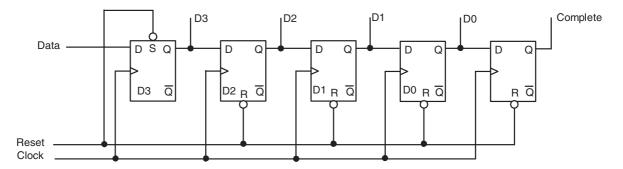

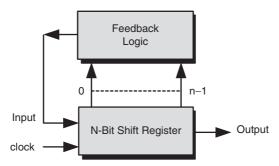

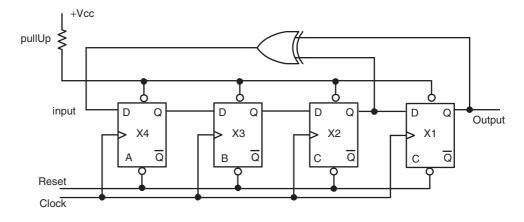

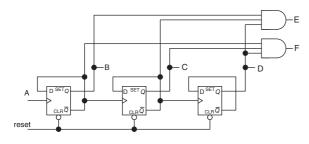

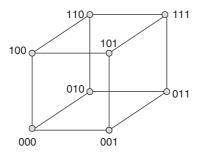

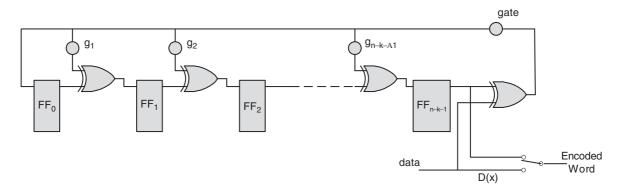

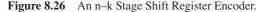

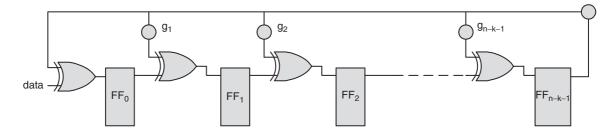

|     | 3.5.3   | Linear Fe    | eedback Shift Registers                           | 122 |

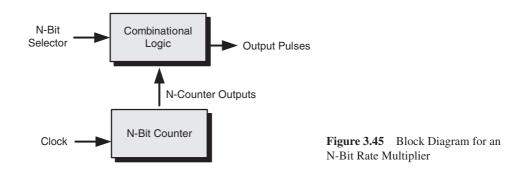

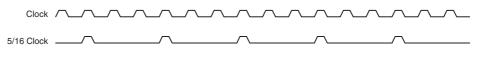

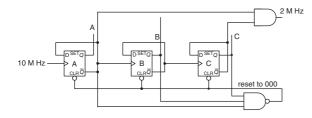

| 3.6 | Design  | ing Finite-S | State Machines – Part 2: Counting and Dividing    | 124 |

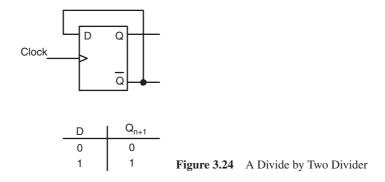

|     | 3.6.1   | Dividers     |                                                   | 124 |

|     |         | 3.6.1.1      | Divide by Two                                     | 124 |

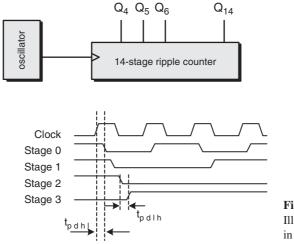

|     | 3.6.2   | Asynchro     | onous Dividers and Counters                       | 125 |

|     | 3.6.3   | Synchror     | nous Dividers and Counters                        | 127 |

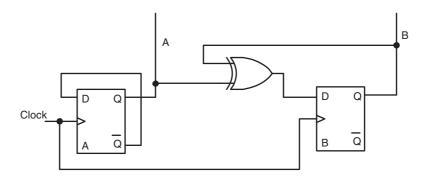

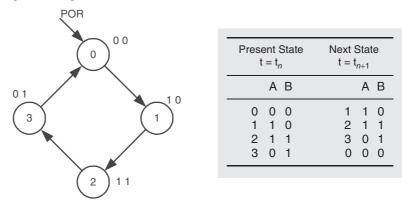

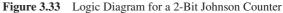

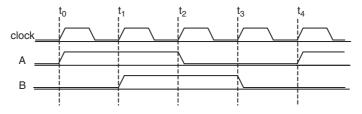

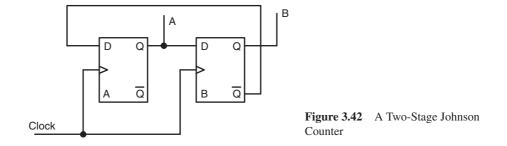

|     | 3.6.4   | Johnson      | Counters                                          | 128 |

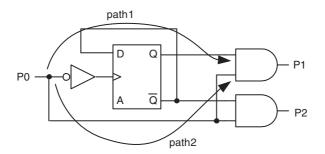

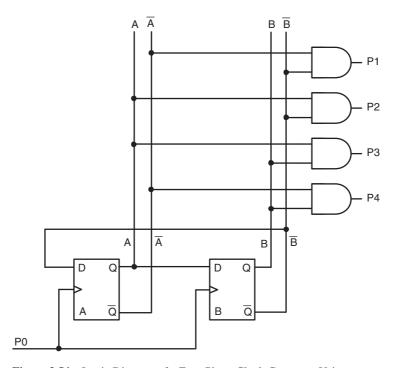

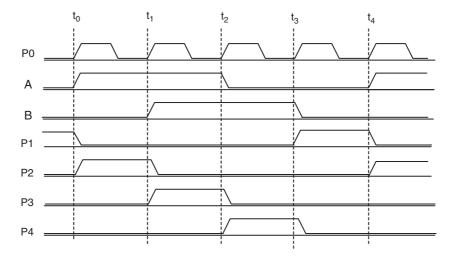

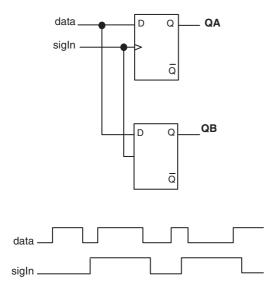

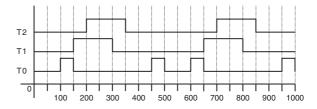

|     |         | 3.6.4.1      | Two-Stage Johnson Counter                         | 129 |

|     |         | 3.6.4.2      | Three- or Greater Stage Johnson Counter           | 130 |

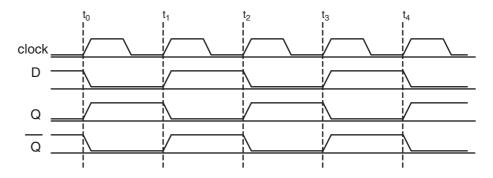

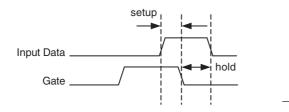

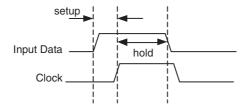

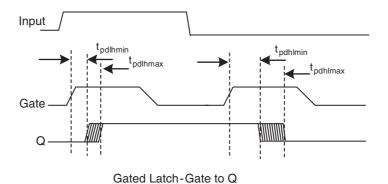

| 3.7 | Practic | al Consider  | ations – Part 1: Timing in Latches and Flip-Flops | 131 |

|     | 3.7.1   | Gated La     | tches                                             | 131 |

|     | 3.7.2   | Flip-Flop    | 98                                                | 132 |

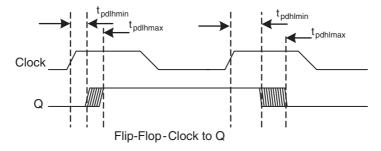

|     | 3.7.3   | Propagat     | ion Delays                                        | 132 |

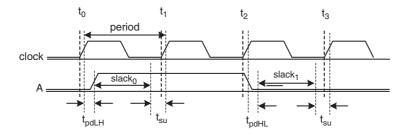

|     | 3.7.4   | Timing N     | <i>A</i> argin                                    | 133 |

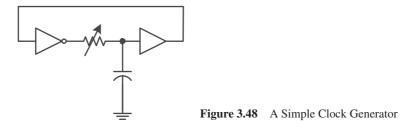

| 3.8 | Practic | al Consider  | ations – Part 2: Clocks and Clock Distribution    | 135 |

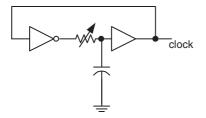

|   |            | 3.8.1      | The Sour                | ce                                      | 135        |

|---|------------|------------|-------------------------|-----------------------------------------|------------|

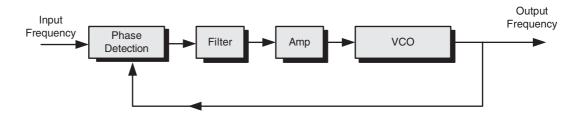

|   |            |            | 3.8.1.1                 | Frequency                               | 135        |

|   |            |            | 3.8.1.2                 | Precision and Stability                 | 137        |

|   |            | 3.8.2      | Designin                | g a Clock System                        | 137        |

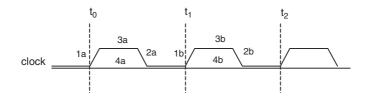

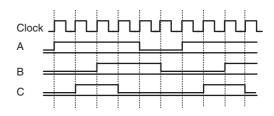

|   |            |            | 3.8.2.1                 | Single-Phase Clocks                     | 137        |

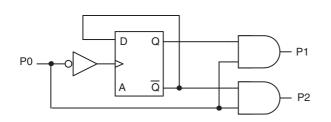

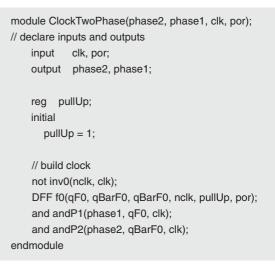

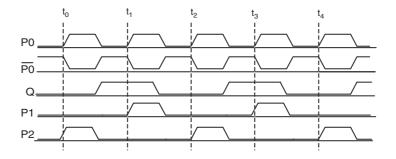

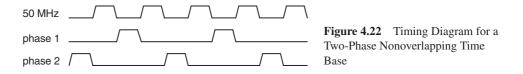

|   |            |            | 3.8.2.2                 | Multiple-Phase Clocks                   | 138        |

|   |            |            | 3.8.2.3                 | More Than Four Phases                   | 141        |

|   |            |            | 3.8.2.4                 | Multiple Clocks Versus Multiple Phases  | 141        |

|   |            |            | 3.8.2.5                 | Gating the Clock                        | 141        |

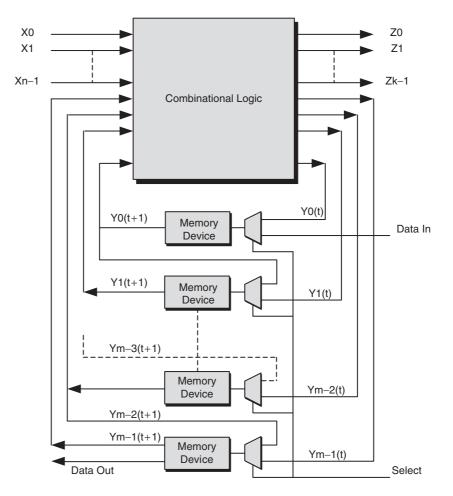

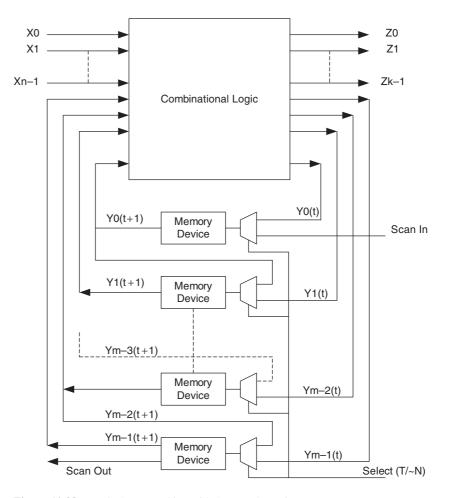

|   | 3.9        | -          | Sequential              |                                         | 141        |

|   |            | 3.9.1      |                         | e-State Machine Model Revisited         | 142        |

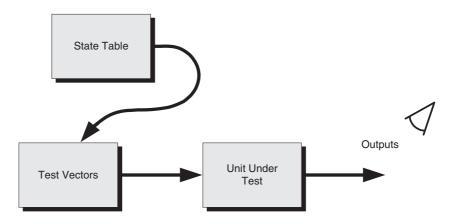

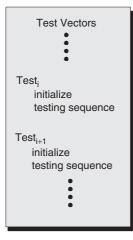

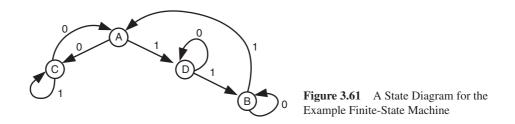

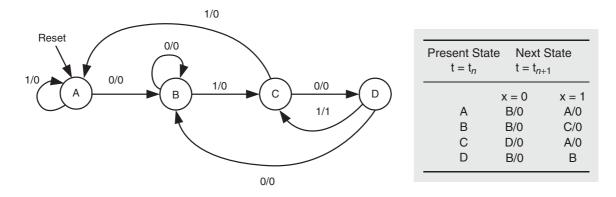

|   |            | 3.9.2      | 1                       | al Circuit Test – A First Look          | 142        |

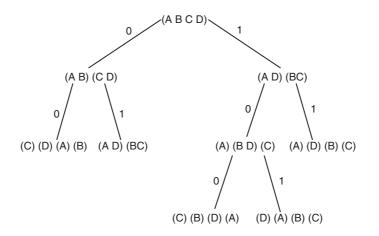

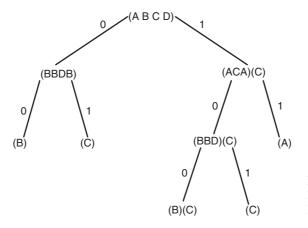

|   |            | 2.0.2      | 3.9.2.1                 | Defining Homing and Transfer Sequences  | 145        |

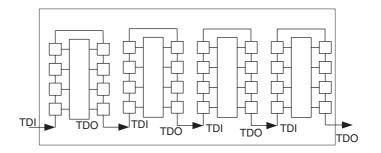

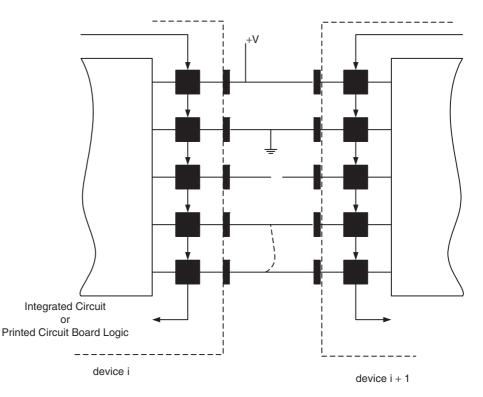

|   |            | 3.9.3      |                         | ign Techniques                          | 148        |

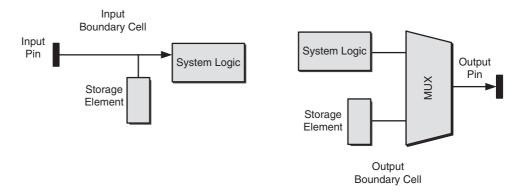

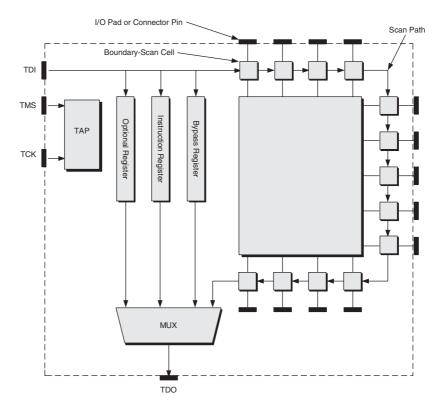

|   | 2.10       | 3.9.4      | -                       | y Scan – Extending Scan-Path Techniques | 149        |

|   | 3.10       | Summa      | •                       |                                         | 152        |

|   | 3.11       |            | Questions               | _                                       | 152        |

|   | 3.12       | -          | t Question              | 8                                       | 153        |

|   | 3.13       | Problem    | ns                      |                                         | 155        |

| 4 | Memor      | ries and t | the Memor               | y Subsystem                             | 165        |

|   | 4.1        | Introdu    | ation                   |                                         | 165        |

|   | 4.1<br>4.2 | Introdu    |                         | 477 7                                   | 165<br>166 |

|   | 4.2<br>4.3 |            | ying Memo<br>eral Memor |                                         | 167        |

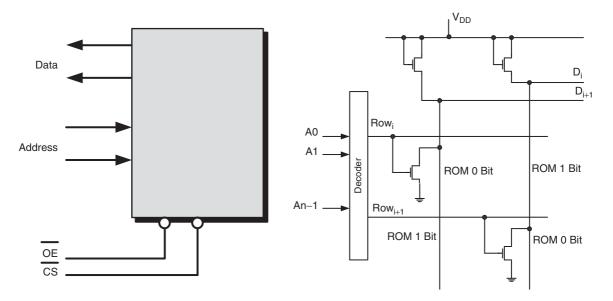

|   | 4.3<br>4.4 |            | Overview                | y interface                             | 167        |

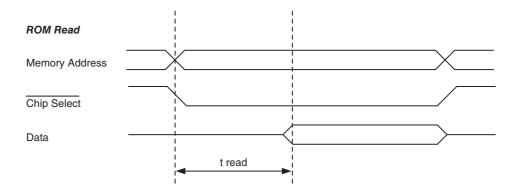

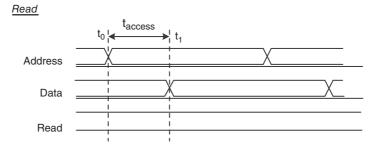

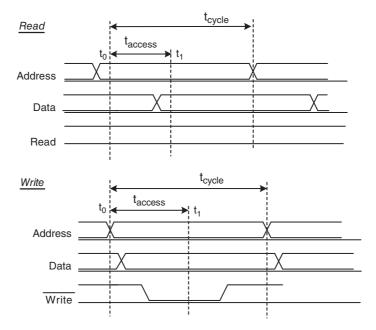

|   | 4.4        | 4.4.1      | Read Ope                | eration                                 | 169        |

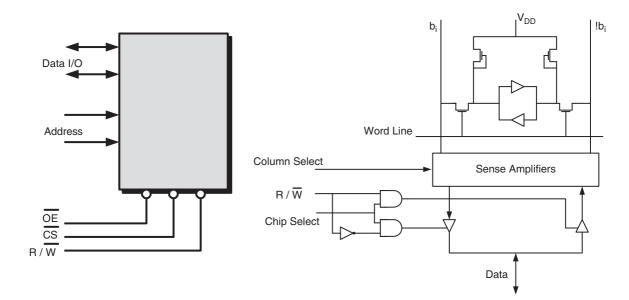

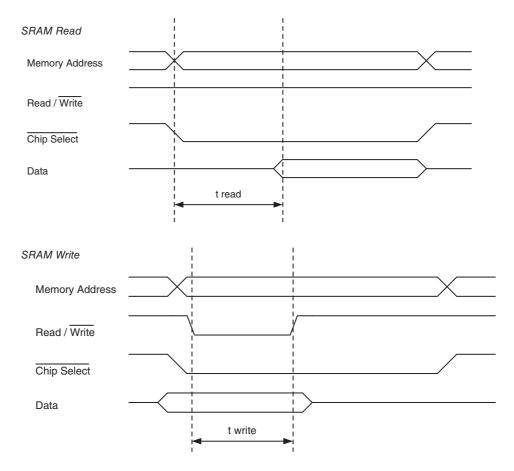

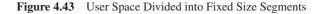

|   | 4.5        |            | RAM Overv               |                                         | 169        |

|   | 1.5        | 4.5.1      |                         |                                         | 171        |

|   |            | 4.5.2      | Read Op                 |                                         | 171        |

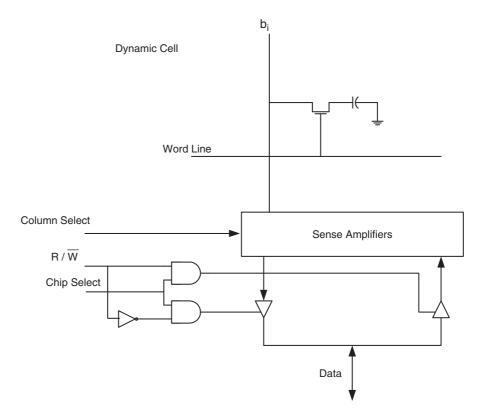

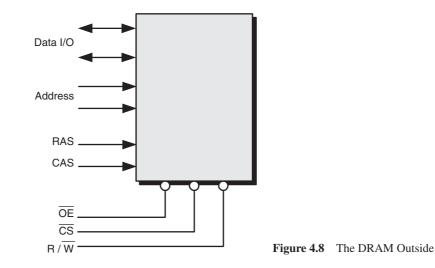

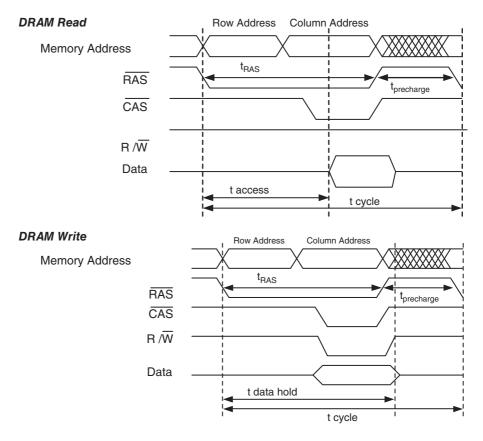

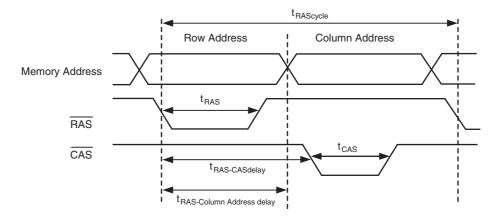

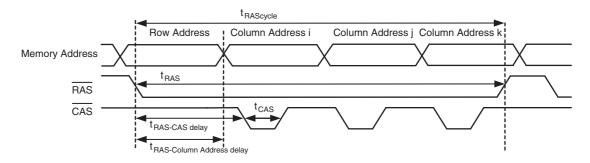

|   | 4.6        |            | ic RAM O                |                                         | 171        |

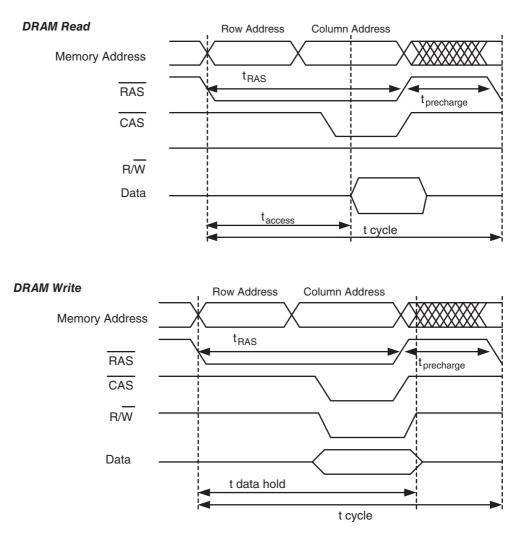

|   |            | 4.6.1      | Read Ope                |                                         | 172        |

|   |            | 4.6.2      | Write Op                |                                         | 172        |

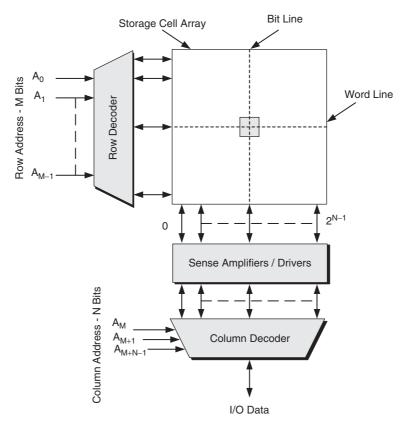

|   |            | 4.6.3      | Refresh (               |                                         | 172        |

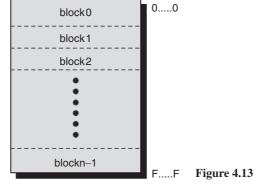

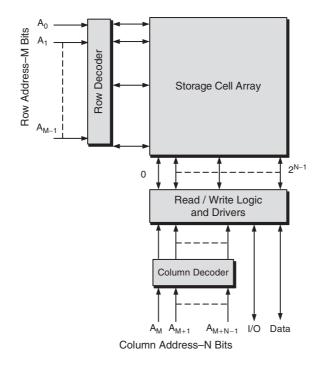

|   | 4.7        | Chip O     | rganization             |                                         | 173        |

|   | 4.8        | Termin     |                         |                                         | 173        |

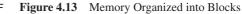

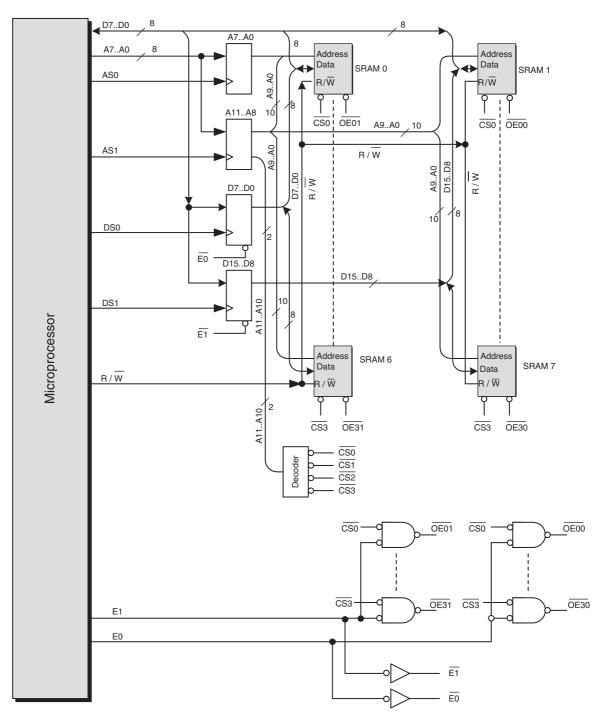

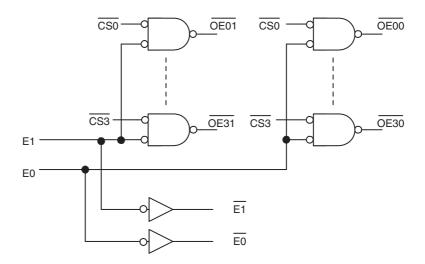

|   | 4.9        | A Mem      | ory Interfa             | ce in Detail                            | 176        |

|   | 4.10       | An SRA     | AM Design               |                                         | 177        |

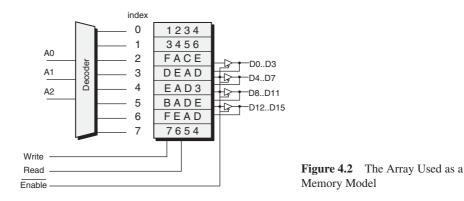

|   |            | 4.10.1     | The Men                 | nory Array                              | 177        |

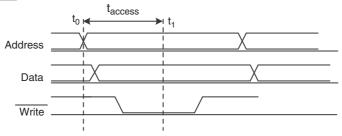

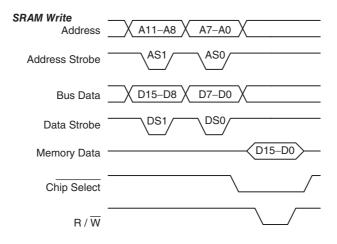

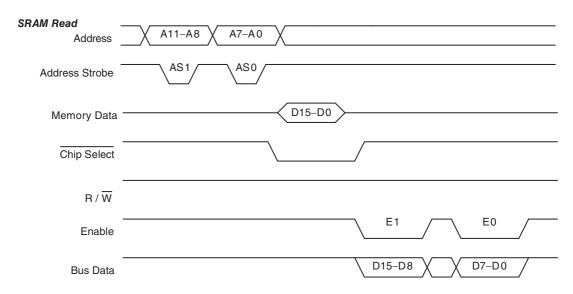

|   |            | 4.10.2     | Reading                 | and Writing                             | 179        |

|   |            | 4.10.3     | Write                   |                                         | 179        |

|   |            | 4.10.4     | Read                    |                                         | 179        |

|   | 4.11       | A DRA      | M Design                |                                         | 180        |

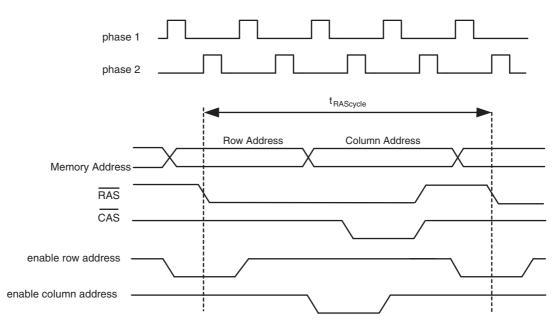

|   |            | 4.11.1     |                         | iming Analysis                          | 181        |

|   |            |            | 4.11.1.1                | Core Components                         | 181        |

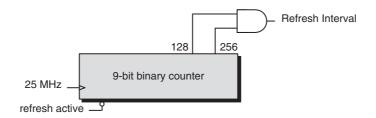

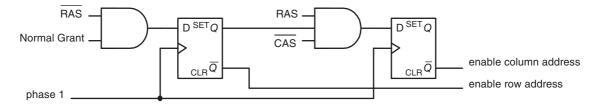

|   |            | 4.11.2     | DRAM F                  |                                         | 182        |

|   | 4.12       |            |                         | bry Interface                           | 183        |

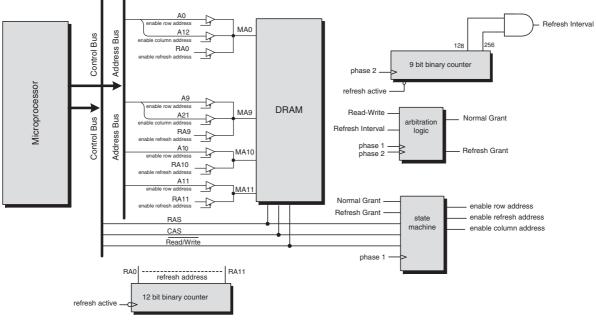

|   |            | 4.12.1     | Refresh 7               |                                         | 183        |

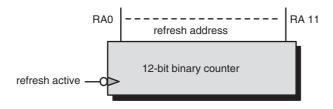

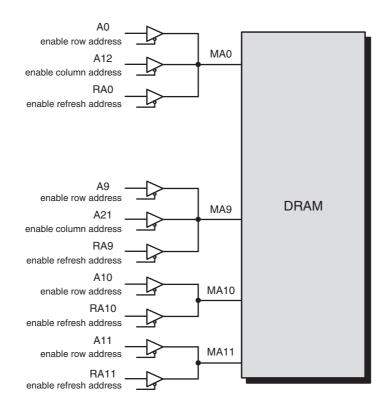

|   |            | 4.12.2     | Refresh A               | Address                                 | 184        |

|   |                                                                             | 4.10.2 Defect Addition                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                                                                                             |

|---|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

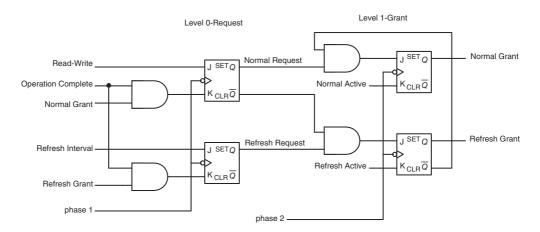

|   | 4.10                                                                        | 4.12.3 Refresh Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                        | 185                                                                                                                                             |

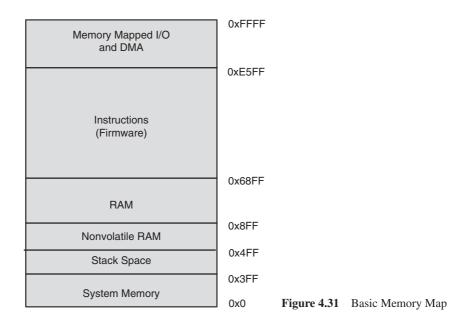

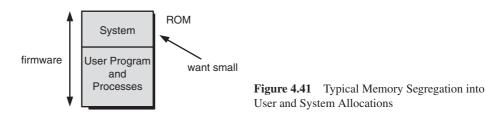

|   | 4.13                                                                        | The Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 188                                                                                                                                             |

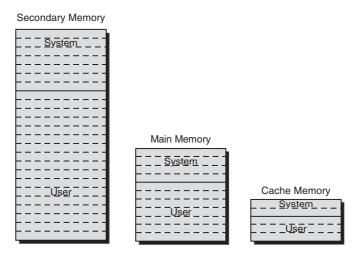

|   | 4.14                                                                        | Memory Subsystem Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                     | 189                                                                                                                                             |

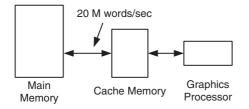

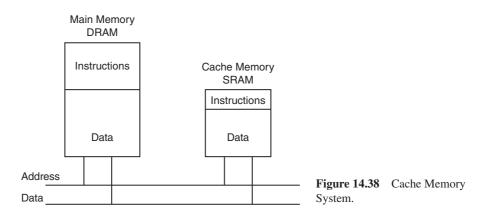

|   | 4.15                                                                        | Basic Concepts of Caching                                                                                                                                                                                                                                                                                                                                                                                                                                         | 190                                                                                                                                             |

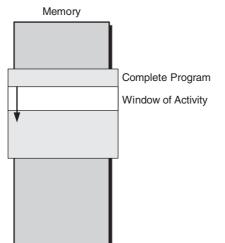

|   |                                                                             | 4.15.1 Locality of Reference                                                                                                                                                                                                                                                                                                                                                                                                                                      | 190                                                                                                                                             |

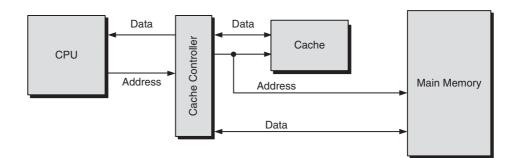

|   |                                                                             | 4.15.2 Cache System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                  | 192                                                                                                                                             |

|   | 4.16                                                                        | Designing a Cache System                                                                                                                                                                                                                                                                                                                                                                                                                                          | 192                                                                                                                                             |

|   |                                                                             | 4.16.1 A High-Level Description                                                                                                                                                                                                                                                                                                                                                                                                                                   | 192                                                                                                                                             |

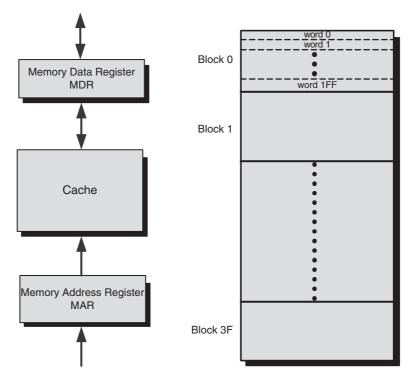

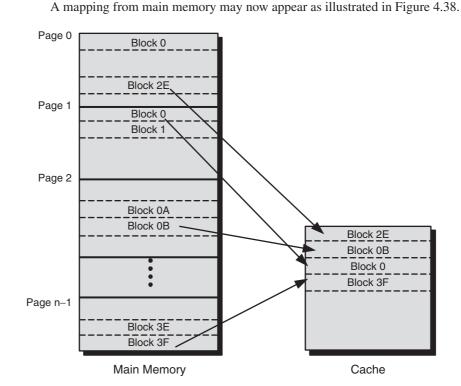

|   | 4.17                                                                        | Caching – A Direct Mapped Implementation                                                                                                                                                                                                                                                                                                                                                                                                                          | 193                                                                                                                                             |

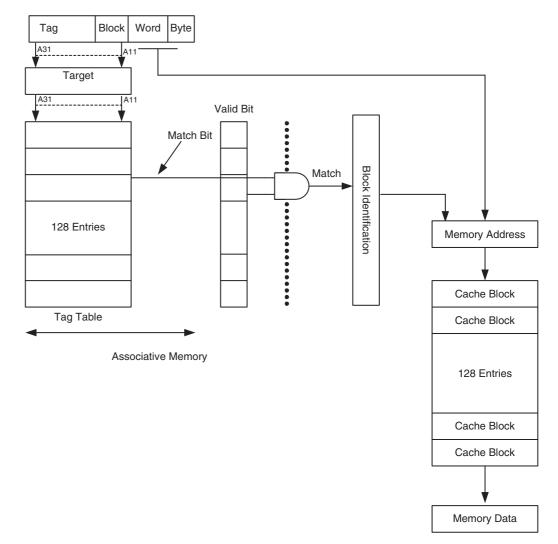

|   | 4.18                                                                        | Caching – An Associative Mapping Cache Implementation                                                                                                                                                                                                                                                                                                                                                                                                             | 196                                                                                                                                             |

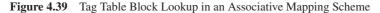

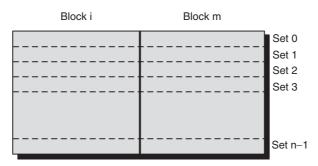

|   | 4.19                                                                        | Caching – A Block-Set Associative Mapping Cache Implementation                                                                                                                                                                                                                                                                                                                                                                                                    | 198                                                                                                                                             |

|   | 4.20                                                                        | Dynamic Memory Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                         | 199                                                                                                                                             |

|   |                                                                             | 4.20.1 Swapping                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200                                                                                                                                             |

|   |                                                                             | 4.20.2 Overlays                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200                                                                                                                                             |

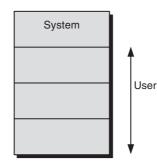

|   |                                                                             | 4.20.3 Multiprogramming                                                                                                                                                                                                                                                                                                                                                                                                                                           | 201                                                                                                                                             |

|   |                                                                             | 4.20.3.1 Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 201                                                                                                                                             |

|   |                                                                             | 4.20.3.2 Variable Number                                                                                                                                                                                                                                                                                                                                                                                                                                          | 202                                                                                                                                             |

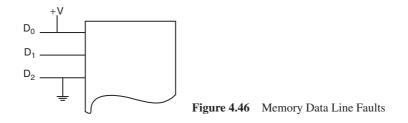

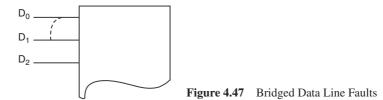

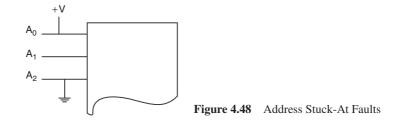

|   | 4.21                                                                        | Testing Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 202                                                                                                                                             |

|   |                                                                             | 4.21.1 RAM Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 204                                                                                                                                             |

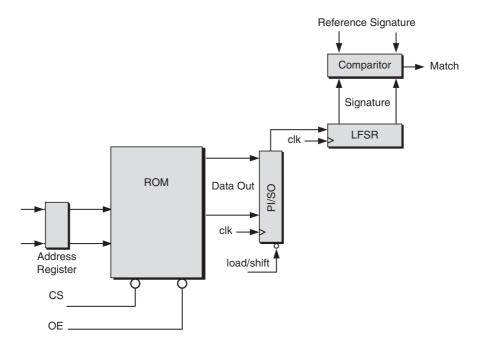

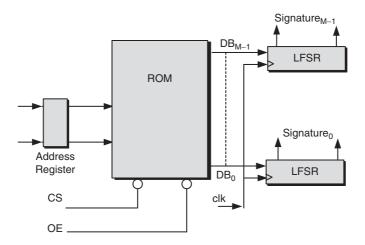

|   |                                                                             | 4.21.2 ROM Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 206                                                                                                                                             |

|   | 4.22                                                                        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 208                                                                                                                                             |

|   | 4.23                                                                        | Review Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 208                                                                                                                                             |

|   | 4.24                                                                        | Thought Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 209                                                                                                                                             |

|   | 4.25                                                                        | Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 210                                                                                                                                             |

|   |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

|   |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| 5 | An Intr                                                                     | roduction to Software Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                    | 215                                                                                                                                             |

| 5 |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| 5 | 5.1                                                                         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 215                                                                                                                                             |

| 5 | 5.1<br>5.2                                                                  | Introduction<br>An Introduction to UML                                                                                                                                                                                                                                                                                                                                                                                                                            | 215<br>216                                                                                                                                      |

| 5 | 5.1<br>5.2<br>5.3                                                           | Introduction<br>An Introduction to UML<br>UML Diagrams                                                                                                                                                                                                                                                                                                                                                                                                            | 215<br>216<br>217                                                                                                                               |

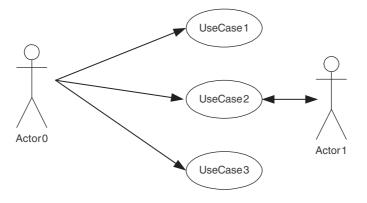

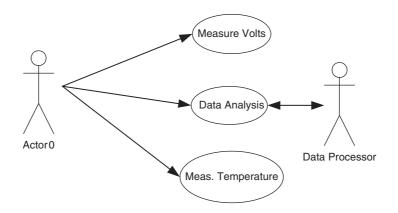

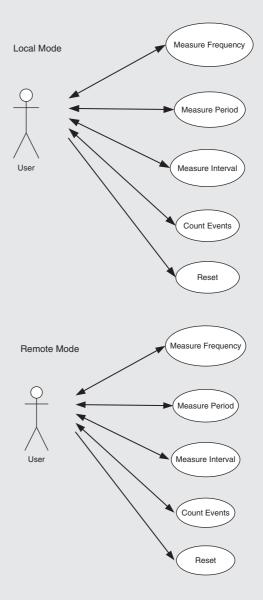

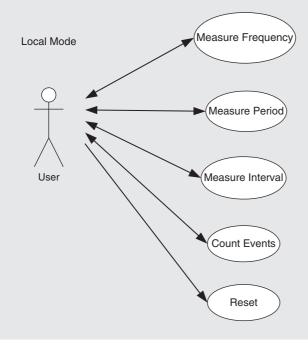

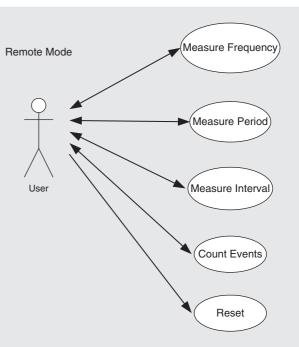

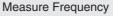

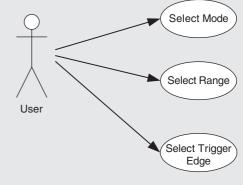

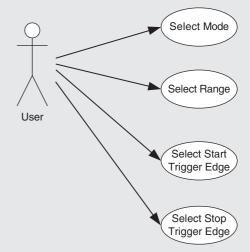

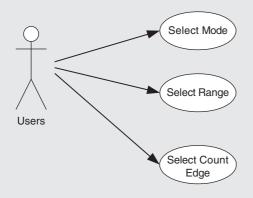

| 5 | 5.1<br>5.2                                                                  | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases                                                                                                                                                                                                                                                                                                                                                                                               | 215<br>216<br>217<br>218                                                                                                                        |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                    | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case                                                                                                                                                                                                                                                                                                                                                                   | 215<br>216<br>217<br>218<br>219                                                                                                                 |

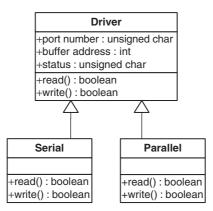

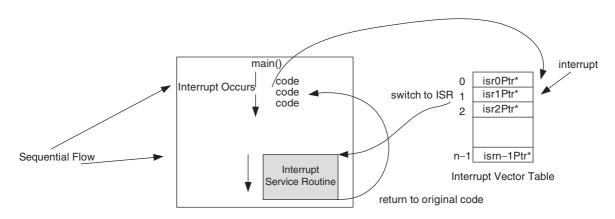

| 5 | 5.1<br>5.2<br>5.3                                                           | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams                                                                                                                                                                                                                                                                                                                                                 | 215<br>216<br>217<br>218<br>219<br>220                                                                                                          |

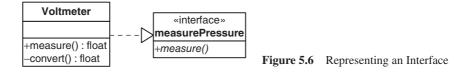

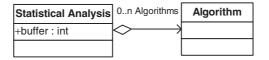

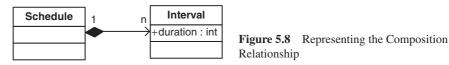

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                    | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships                                                                                                                                                                                                                                                                                                                    | 215<br>216<br>217<br>218<br>219<br>220<br>221                                                                                                   |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                    | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization                                                                                                                                                                                                                                                                           | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221                                                                                            |

| 5 | 5.1<br>5.2<br>5.3<br>5.4                                                    | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface                                                                                                                                                                                                                                                      | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221                                                                                     |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                             | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment                                                                                                                                                                                                                               | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222                                                                              |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                             | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML                                                                                                                                                                                                  | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>221<br>222<br>223                                                                |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                             | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams                                                                                                                                                                          | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>221<br>222<br>223<br>223                                                         |

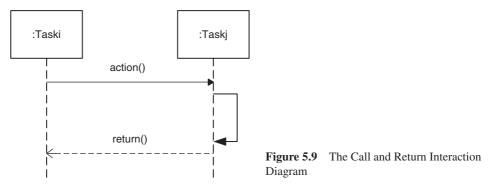

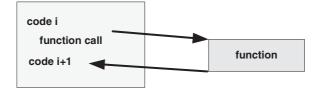

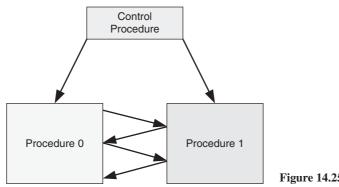

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                             | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return                                                                                                                                                 | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>221<br>222<br>223<br>223<br>224                                                  |

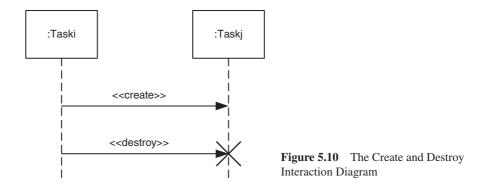

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                             | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy                                                                                                                     | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224                                           |

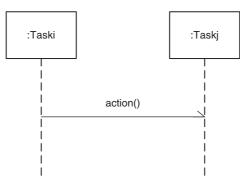

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                               | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send                                                                                                       | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>225                                    |

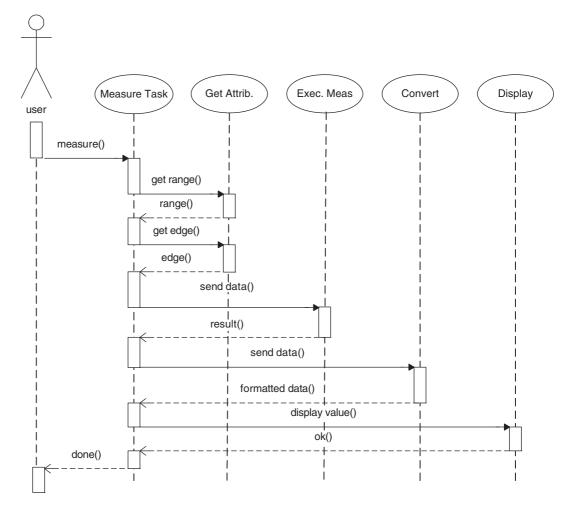

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                        | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams                                                                                  | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>225<br>225                             |

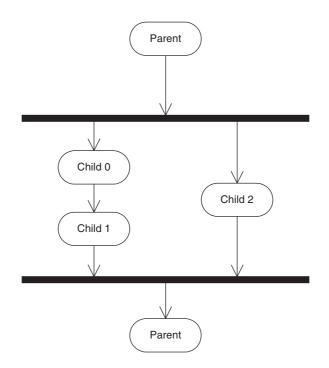

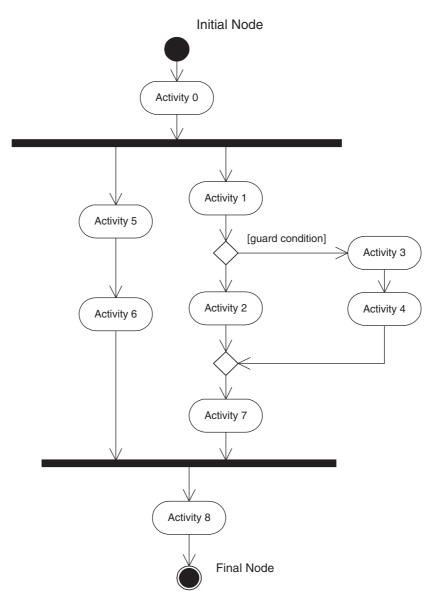

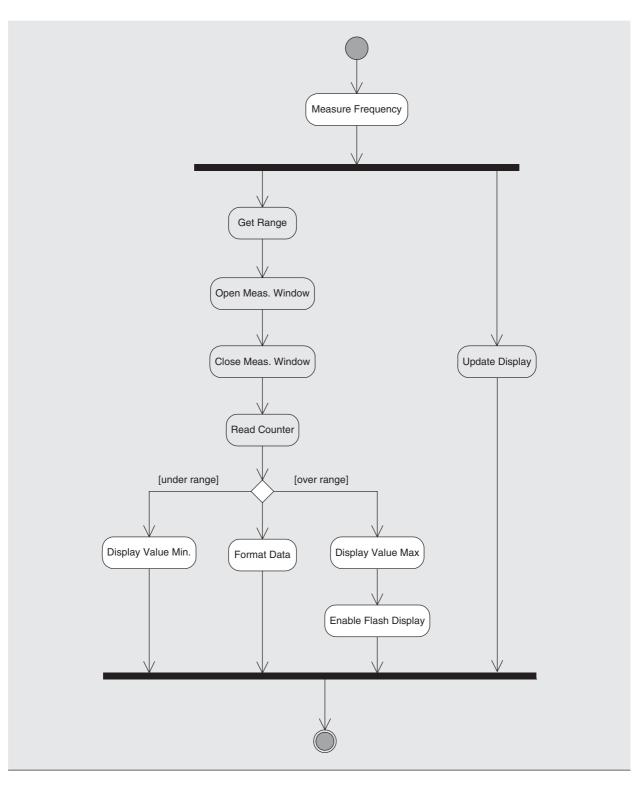

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                 | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams<br>Fork and Join                                                                 | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>225<br>225<br>226                      |

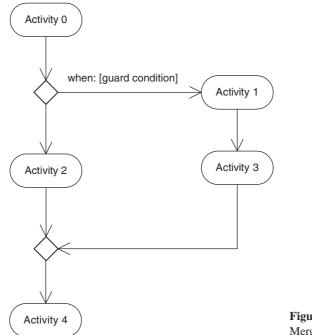

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10         | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams<br>Fork and Join<br>Branch and Merge                                             | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>225<br>225<br>226<br>227               |

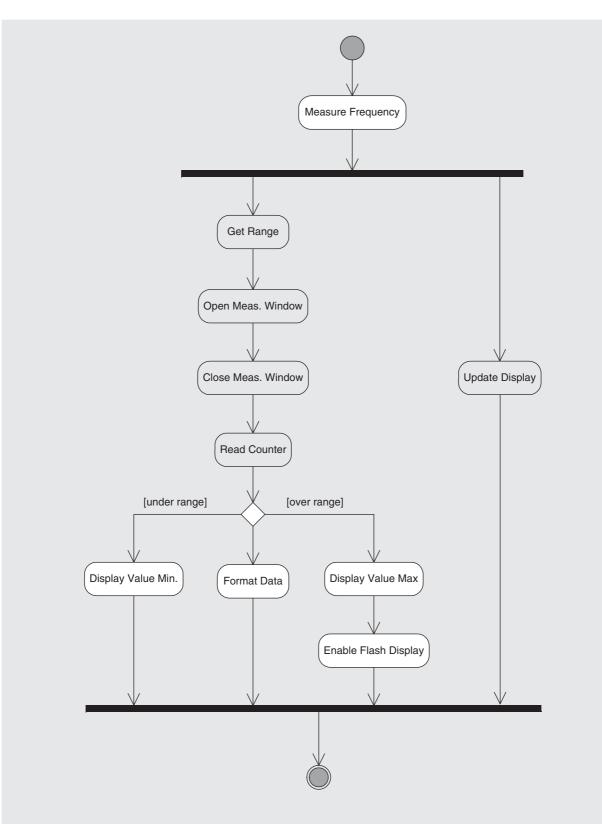

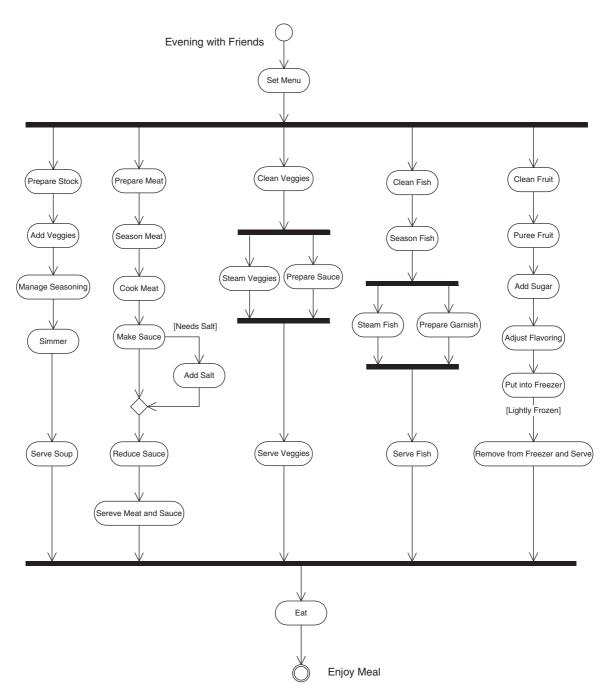

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams<br>Fork and Join<br>Branch and Merge<br>Activity Diagram                         | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>224<br>224<br>225<br>225<br>226<br>227<br>228               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10         | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams<br>Fork and Join<br>Branch and Merge<br>Activity Diagram<br>State Chart Diagrams | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>225<br>225<br>226<br>227<br>228<br>228 |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | Introduction<br>An Introduction to UML<br>UML Diagrams<br>Use Cases<br>5.4.1 Writing a Use Case<br>Class Diagrams<br>5.5.1 Class Relationships<br>5.5.1.1 Inheritance or Generalization<br>5.5.1.2 Interface<br>5.5.1.3 Containment<br>Dynamic Modeling with UML<br>Interaction Diagrams<br>5.7.1 Call and Return<br>5.7.2 Create and Destroy<br>5.7.3 Send<br>Sequence Diagrams<br>Fork and Join<br>Branch and Merge<br>Activity Diagram                         | 215<br>216<br>217<br>218<br>219<br>220<br>221<br>221<br>221<br>222<br>223<br>223<br>224<br>224<br>225<br>225<br>226<br>227<br>228               |

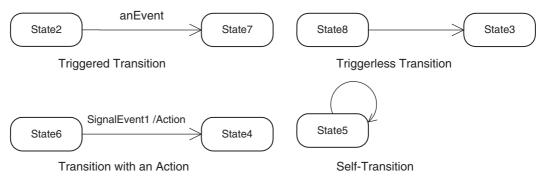

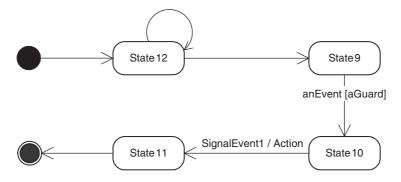

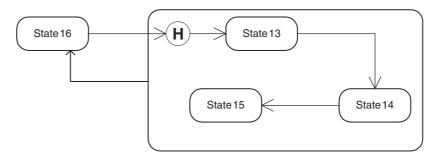

|   |       |           | 5.12.2.1     | UML State Chart Diagrams                     | 230 |

|---|-------|-----------|--------------|----------------------------------------------|-----|

|   |       |           | 5.12.2.2     |                                              | 230 |

|   |       |           | 5.12.2.3     | Guard Conditions                             | 231 |

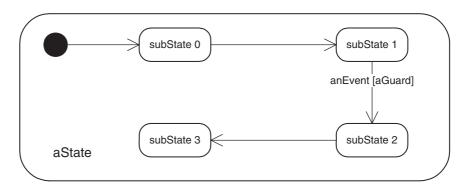

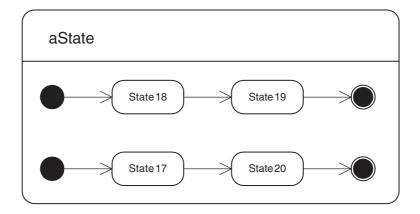

|   |       |           | 5.12.2.4     | Composite States                             | 232 |

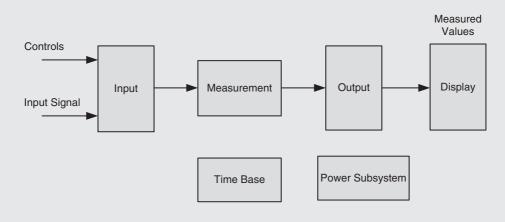

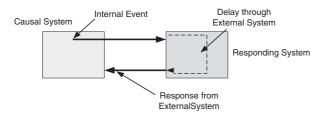

|   | 5.13  | Dynam     | ic Modeling  | g with Structured Design Methods             | 233 |

|   |       | 5.13.1    | Brief Intr   | oduction to the Structured Design Philosophy | 233 |

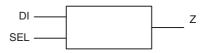

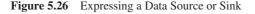

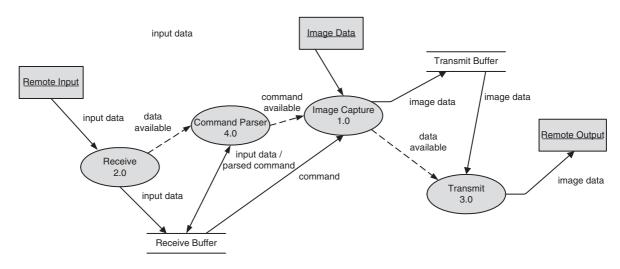

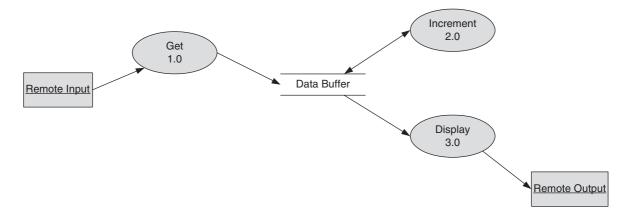

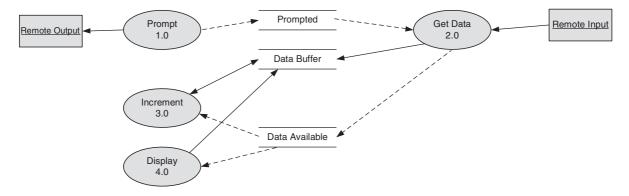

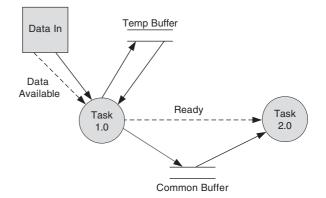

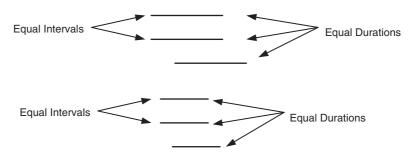

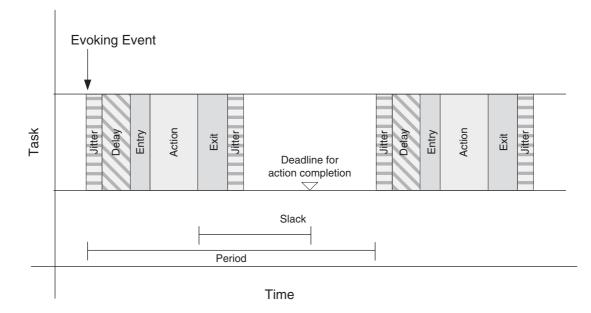

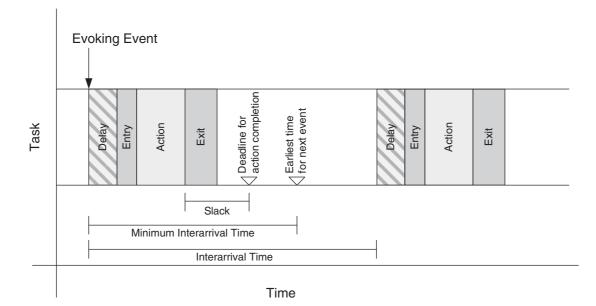

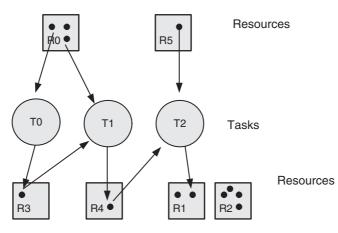

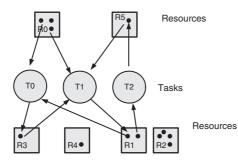

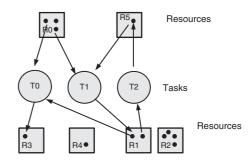

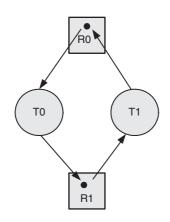

|   |       | 5.13.2    | Data and     | Control Flow Diagrams                        | 234 |

|   |       |           | 5.13.2.1     | The Elements                                 | 234 |

|   | 5.14  | Summa     | ary          |                                              | 237 |

|   | 5.15  | Review    | Questions    |                                              | 237 |

|   | 5.16  | Though    | nt Questions | 3                                            | 239 |

|   | 5.17  | Probler   | ns           |                                              | 240 |

| 6 | The S | oftware S | ide – Part   | 1: The C Program                             | 243 |

|   | 6.1   | Introdu   | ction        |                                              | 243 |

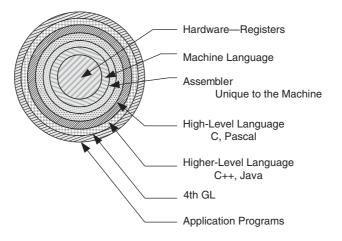

|   | 6.2   | Softwa    |              | lanifestations                               | 243 |

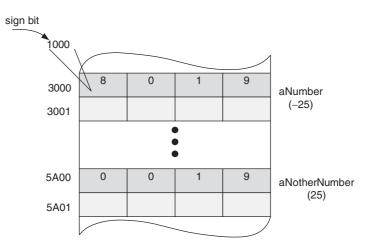

|   |       | 6.2.1     |              | ng Hardware and Software                     | 244 |

|   |       | 6.2.2     | -            | el Language                                  | 245 |

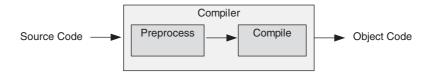

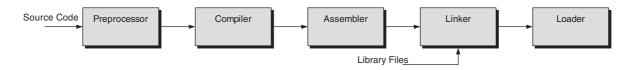

|   |       | 6.2.3     | Preproces    |                                              | 245 |

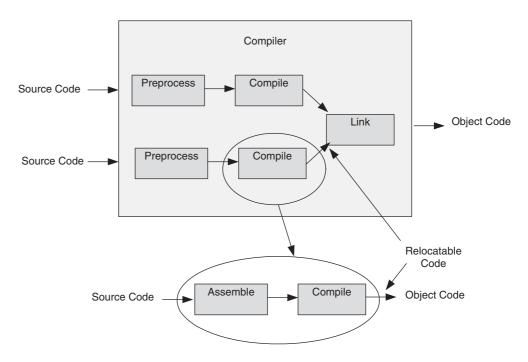

|   |       | 6.2.4     | Cross Cor    |                                              | 246 |

|   |       | 6.2.5     |              |                                              | 246 |

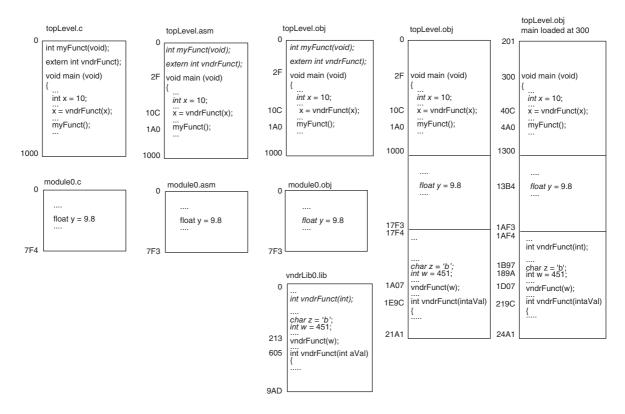

|   |       | 6.2.6     | Linker an    | d Loader                                     | 247 |

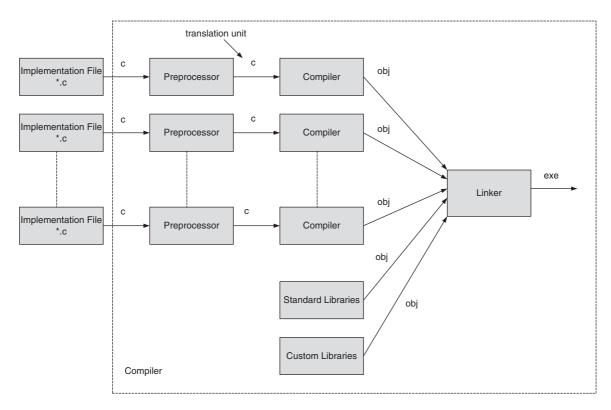

|   |       | 6.2.7     | Storing      |                                              | 248 |

|   | 6.3   |           | bedded C P   | -                                            | 249 |

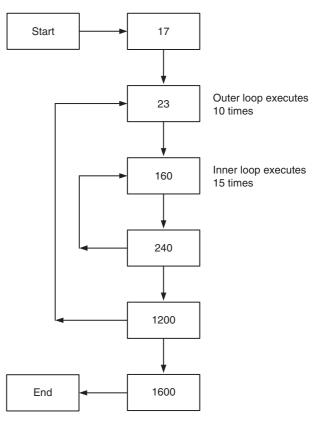

|   |       | 6.3.1     | A Program    |                                              | 249 |

|   |       | 6.3.2     | 1            | ng Embedded Software                         | 249 |

|   |       |           | 6.3.2.1      | Abstraction                                  | 250 |

|   | 6.4   |           | ling Blocks  |                                              | 250 |

|   |       | 6.4.1     |              | ntal Data – What's in a Name?                | 250 |

|   |       |           | 6.4.1.1      | Identifiers in C                             | 250 |

|   |       | 6.4.2     | -            | Variables – Giving Them a Name and a Value   | 251 |

|   |       | 6.4.3     | -            | Variables – Giving Them a Type, Scope, and   |     |

|   |       |           | Storage C    |                                              | 252 |

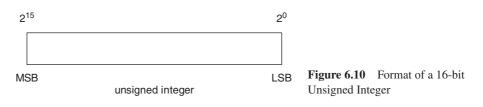

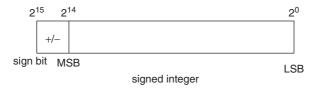

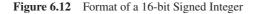

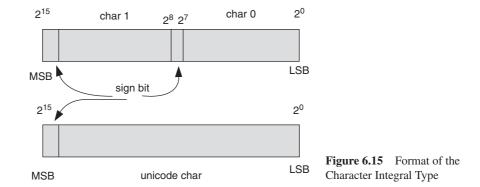

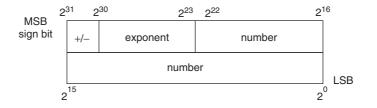

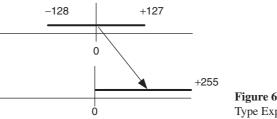

|   |       |           | 6.4.3.1      | Туре                                         | 252 |

|   |       |           | 6.4.3.2      | The const Qualifier                          | 258 |

|   |       |           | 6.4.3.3      | Variable Names Revisited                     | 259 |

|   |       |           | 6.4.3.4      | Type Conversions                             | 259 |

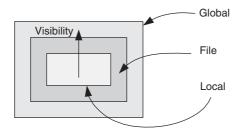

|   |       |           | 6.4.3.5      | Scope                                        | 261 |

|   |       |           | 6.4.3.6      | Storage Class                                | 263 |

|   | 6.5   | -         | ram Structu  |                                              | 268 |

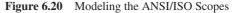

|   |       | 6.5.1     | -            | Compilation                                  | 268 |

|   |       | 6.5.2     | Translatio   |                                              | 268 |

|   |       | 6.5.3     | U            | nd Linkage                                   | 269 |

|   |       |           | 6.5.3.1      | Linking                                      | 269 |

|   |       |           | 6.5.3.2      | Linkage                                      | 270 |

|   |       | 6.5.4     |              | Finds Functions                              | 271 |

|   |       | 6.5.5     | Makefiles    |                                              | 271 |

|   |       | 6.5.6     | Standard     | and Custom Libraries                         | 272 |

|   |       | 6.5.7      | Debug and Relea                | se Builds               | 272        |

|---|-------|------------|--------------------------------|-------------------------|------------|

|   | 6.6   | Summ       | ary                            |                         | 273        |

|   | 6.7   | Review     | Questions                      |                         | 273        |

|   | 6.8   | Thoug      | nt Questions                   |                         | 274        |

|   | 6.9   | Proble     | ns                             |                         | 275        |

| 7 | The S | Software S | ide – Part 2: Poin             | ters and Functions      | 279        |

|   | 7.1   | Introdu    | ction                          |                         | 279        |

|   | 7.2   | Bitwis     | e Operators                    |                         | 280        |

|   |       | 7.2.1      | Bit Manipulation               |                         | 280        |

|   |       | 7.2.2      |                                | g, and Setting Bits     | 281        |

|   |       | 7.2.3      | Arithmetic Opera               |                         | 284        |

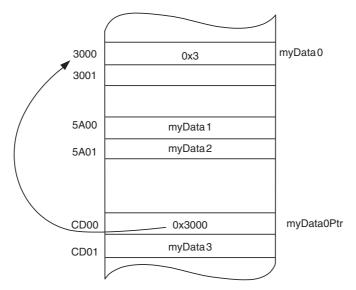

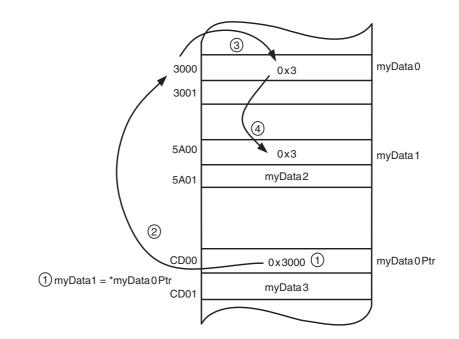

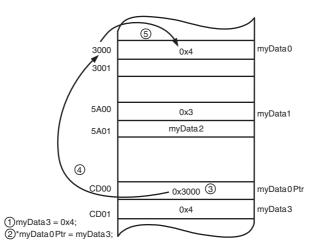

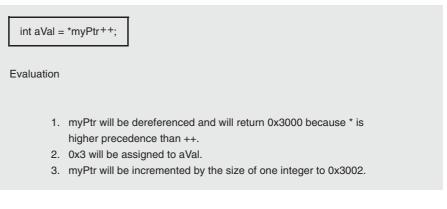

|   | 7.3   |            | Variables and Mer              | nory Addresses          | 285        |

|   |       | 7.3.1      | Getting Started                |                         | 285        |

|   |       | 7.3.2      | Simple Pointer A               |                         | 290        |

|   |       |            |                                | er Comparison           | 293        |

|   |       | 7.3.3      | Const Pointers                 |                         | 293        |

|   |       | 7.3.4      | Generic and NUI                |                         | 294        |

|   |       |            |                                | ric Pointers            | 294        |

|   | 74    | The D      |                                | Pointers                | 295        |

|   | 7.4   | The Fu     |                                | ion Header              | 296<br>296 |

|   |       |            |                                | ion Name                | 296<br>296 |

|   |       |            |                                | nents or Parameter List | 296<br>296 |

|   |       |            | 7.4.1.3 Algui<br>7.4.1.4 Retur |                         | 290<br>296 |

|   |       |            |                                | unction Body            | 290<br>297 |

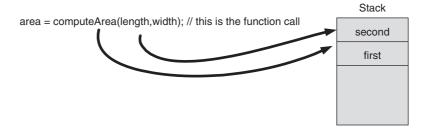

|   |       | 7.4.2      | Using a Function               |                         | 297        |

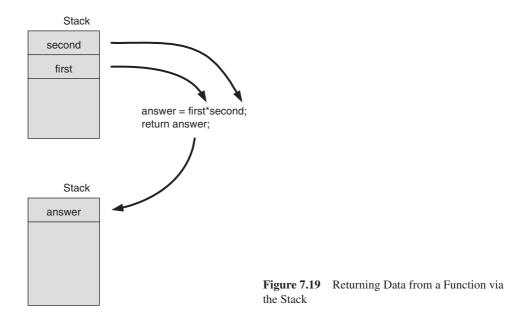

|   |       | 7.4.3      | Pass By Value                  |                         | 301        |

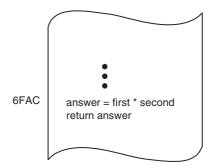

|   |       | 7.4.4      | Pass By Reference              | re.                     | 303        |

|   |       | 7.4.5      | Function Name S                |                         | 304        |

|   |       | 7.4.6      | Function Prototy               | -                       | 304        |

|   |       | 7.4.7      | Nesting Function               | =                       | 306        |

|   | 7.5   |            | s to Functions                 |                         | 306        |

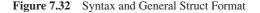

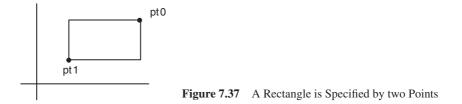

|   | 7.6   | Structu    |                                |                         | 310        |

|   |       | 7.6.1      | The Struct                     |                         | 311        |

|   |       | 7.6.2      | Initialization                 |                         | 313        |

|   |       | 7.6.3      | Access                         |                         | 313        |

|   |       | 7.6.4      | Operations                     |                         | 314        |

|   |       | 7.6.5      | Structs as Data N              | Iembers                 | 314        |

|   |       |            | 7.6.5.1 Acces                  | sing Members            | 314        |

|   |       |            | 7.6.5.2 Initial                | ization and Assignment  | 315        |

|   |       |            | 7.6.5.3 Funct                  | ions                    | 315        |

|   |       | 7.6.6      | Pointers to Struct             | ts                      | 318        |

|   |       |            | 7.6.6.1 Acces                  | sing Members            | 318        |

|   |       | 7.6.7      | Passing Structs a              | nd Pointers to Structs  | 319        |

|   | 7.7   | The In     | 1                              |                         | 320        |

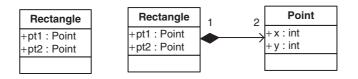

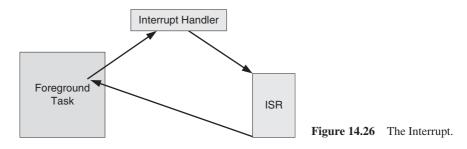

|   |       | 7.7.1      | The Interrupt Co               |                         | 320        |

|   |       | 7.7.2      | The Interrupt Eve              | ent                     | 320        |

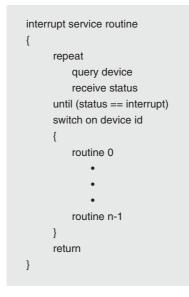

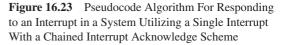

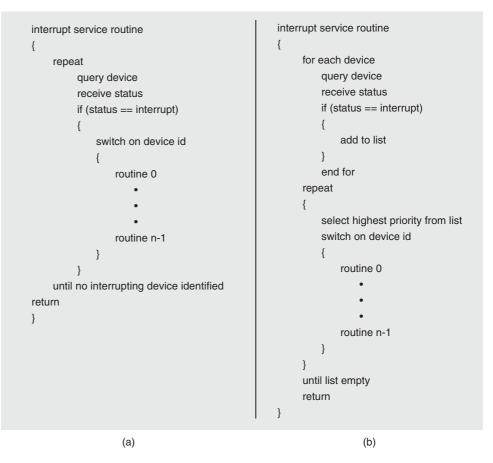

|      | 7.7.3    | The Interr | upt Service Routine – ISR                      | 321 |

|------|----------|------------|------------------------------------------------|-----|

|      | 7.7.4    | The Interr | upt Vector Table                               | 321 |

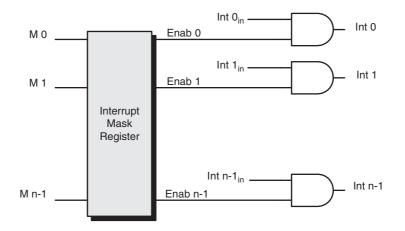

|      | 7.7.5    | Control of | the Interrupt                                  | 323 |

|      |          | 7.7.5.1    | Enable–Disable                                 | 323 |

|      |          | 7.7.5.2    | Recognizing an Interrupting Event              | 323 |

|      |          | 7.7.5.3    | Interrupting and Masking an Interrupting Event | 324 |

| 7.8  | Summary  | /          |                                                | 324 |

| 7.9  | Review Q | Questions  |                                                | 324 |

| 7.10 | Thought  | Questions  |                                                | 326 |

| 7.11 | Problems | 5          |                                                | 327 |

## Part 2 Developing the Foundation

| 8 | Safety, Security, Reliability, and Robust Design |           |                                                 |                     | 331 |

|---|--------------------------------------------------|-----------|-------------------------------------------------|---------------------|-----|

|   | 8.1                                              | Introdu   | tion                                            |                     | 331 |

|   | 8.2                                              | Safety    |                                                 |                     | 333 |

|   | 8.3                                              | Reliabil  | ty                                              |                     | 334 |

|   | 8.4                                              | Faults, 1 | rrors, and Failures                             |                     | 336 |

|   | 8.5                                              | Another   | Look at Reliability                             |                     | 337 |

|   | 8.6                                              | Some R    | eal-World Examples                              |                     | 337 |

|   |                                                  | 8.6.1     | Big Word Small Register                         | r                   | 338 |

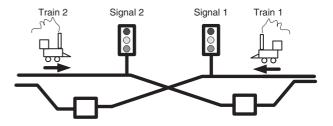

|   |                                                  | 8.6.2     | It's My Turn – Not Yours                        |                     | 338 |

|   |                                                  | 8.6.3     | Where Do I Put My Stuff?                        |                     | 339 |

|   | 8.7                                              | Single-l  | oint and Common Mode Fail                       | ure Model           | 340 |

|   | 8.8                                              | Safe Sp   | cifications                                     |                     | 340 |

|   | 8.9                                              | Safe, Se  | cure, and Robust Designs                        |                     | 341 |

|   |                                                  | 8.9.1     | Understanding System Requ                       | irements            | 341 |

|   |                                                  | 8.9.2     | Managing Essential Informa                      | tion                | 342 |

|   |                                                  | 8.9.3     | The Review Process                              |                     | 343 |

|   |                                                  | 8.9.4     | Bug Lists                                       |                     | 344 |

|   |                                                  | 8.9.5     | Errors and Exceptions                           |                     | 344 |

|   |                                                  | 8.9.6     | Use the Available Tools                         |                     | 347 |

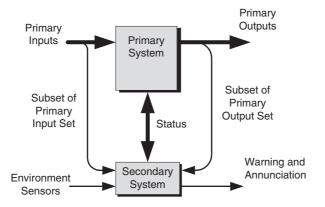

|   | 8.10                                             | Safe and  | Robust Designs - The Syste                      | m                   | 347 |

|   | 8.11                                             | System    | Functional Level Consideration                  | ons                 | 347 |

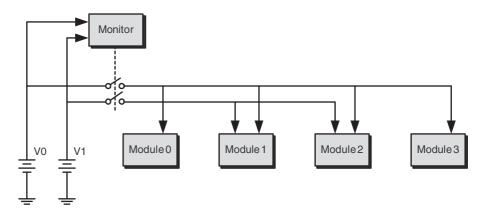

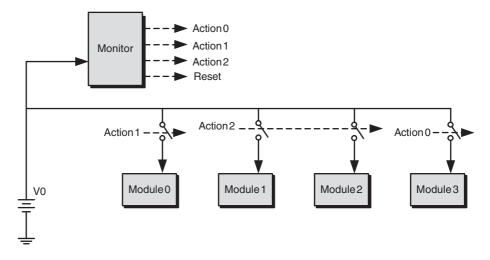

|   |                                                  | 8.11.1    | Control and Alarm Subsyste                      | ms                  | 347 |

|   |                                                  | 8.11.2    | Memory and Bus Subsystem                        | 18                  | 348 |

|   |                                                  | 8.11.3    | Data Faults and the Commun                      | nications Subsystem | 349 |

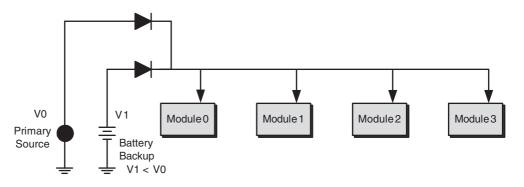

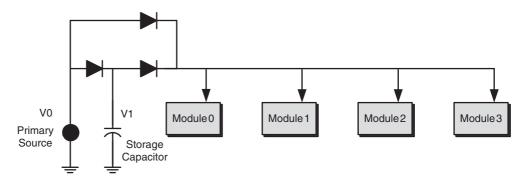

|   |                                                  | 8.11.4    | Power and Reset Subsystem                       | S                   | 349 |

|   |                                                  | 8.11.5    | Peripheral Device Subsystem                     | ns                  | 349 |

|   |                                                  | 8.11.6    | Clock Subsystem                                 |                     | 349 |

|   | 8.12                                             | System    | Architecture Level Considera                    | tions               | 350 |

|   |                                                  | 8.12.1    | Fail Operational <sup>2</sup> /Fail Operational | tional Capability   | 350 |

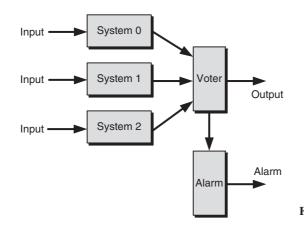

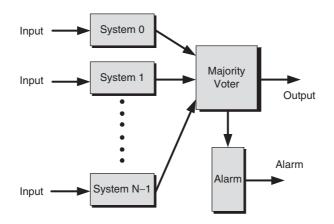

|   |                                                  |           | 8.12.1.1 Same Design                            |                     | 351 |

|   |                                                  |           | 8.12.1.2 Alternative Desig                      | gns                 | 351 |

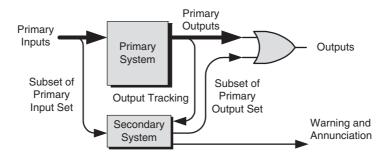

|   |                                                  | 8.12.2    | Reduced Capability                              |                     | 352 |

|      |                  | 8.12.2.1              | Lightweight Redundancy                     | 352        |

|------|------------------|-----------------------|--------------------------------------------|------------|

|      |                  | 8.12.2.2              | Monitor Only                               | 352        |

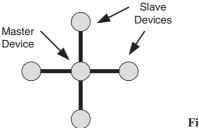

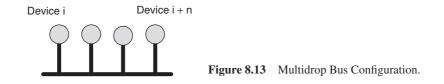

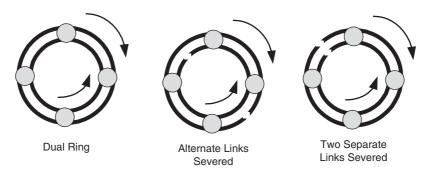

| 8.13 | Busses           | - The Subsy           | ystem Interconnect                         | 353        |

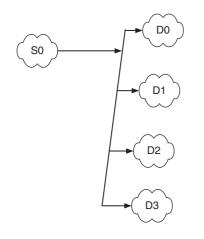

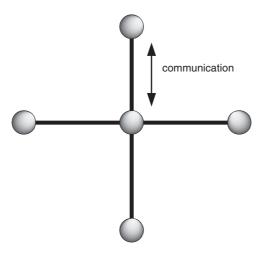

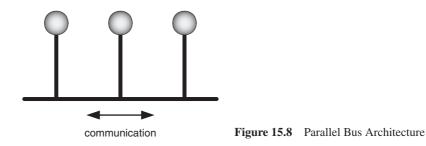

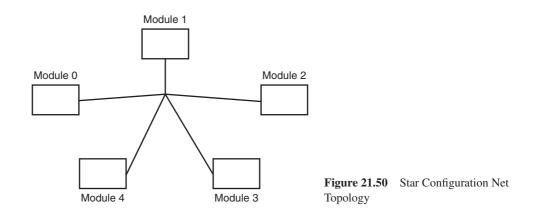

|      | 8.13.1           | The Star C            | Configuration                              | 353        |

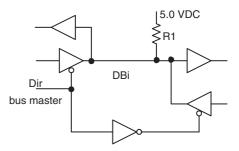

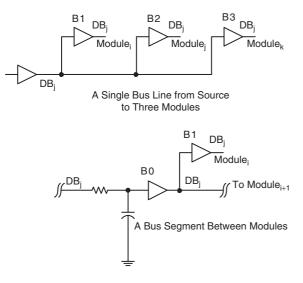

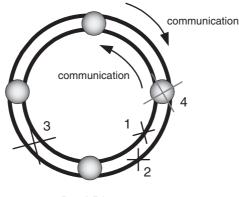

|      | 8.13.2           | The Multi             | drop Bus Configuration                     | 353        |

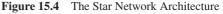

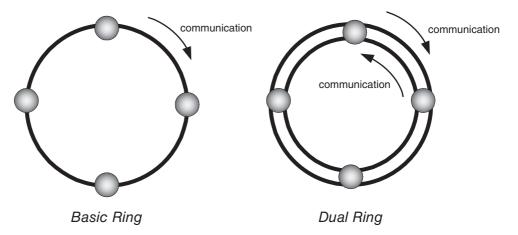

|      | 8.13.3           | The Ring              | Configuration                              | 354        |

| 8.14 | Data an          | d Control F           | aults – Data Boundary Values               | 355        |

|      | 8.14.1           | Type Cont             |                                            | 355        |

|      | 8.14.2           | Boundary              |                                            | 355        |

| 8.15 |                  |                       | aults – The Communications Subsystem       | 356        |

|      | 8.15.1           | Damaged               |                                            | 356        |

|      |                  | 8.15.1.1              | Detectability                              | 356        |

|      |                  | 8.15.1.2              |                                            | 357        |

|      |                  | 8.15.1.3              | 1                                          | 358        |

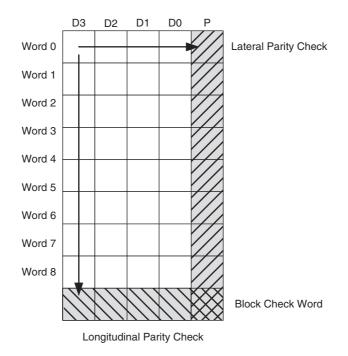

|      | 8.15.2           |                       | Damaged Data                               | 358        |

|      |                  | 8.15.2.1              | Parity                                     | 358        |

| 0.16 |                  | 8.15.2.2              | Linear Codes                               | 358        |

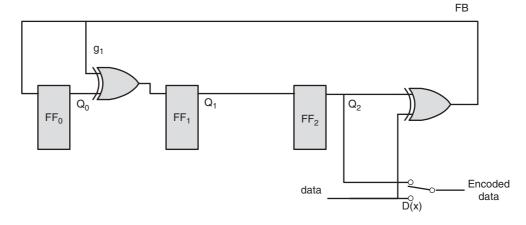

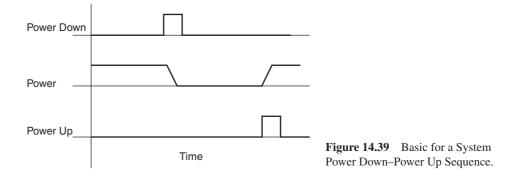

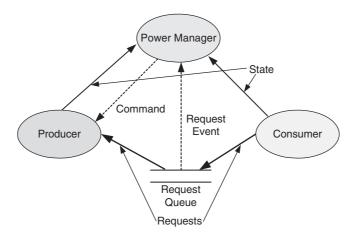

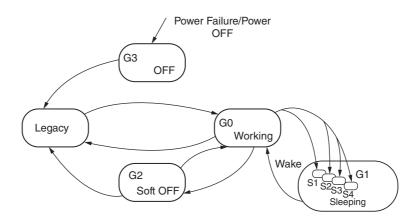

| 8.16 |                  | wer Subsyst           |                                            | 367        |

|      | 8.16.1<br>8.16.2 | Full Opera            |                                            | 368        |

|      | 8.16.2<br>8.16.3 | Reduced (<br>Backup O |                                            | 368<br>369 |

| 8.17 |                  |                       | – Built-in Self-Test (BIST)                | 309        |

| 0.17 | 8.17.1           |                       |                                            | 370        |

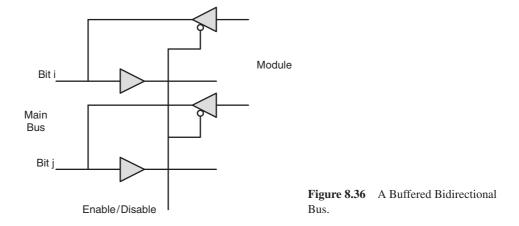

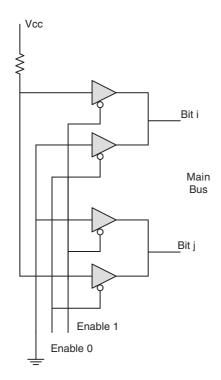

|      |                  | Busses                |                                            | 370        |

|      |                  | ROM Mei               | mory                                       | 373        |

|      | 8.17.4           | RAM Mer               |                                            | 373        |

|      | 0.17.1           | 8.17.4.1              | Peripheral Devices                         | 373        |

|      |                  | 8.17.4.2              | What to Do If a Test Fails?                | 373        |

| 8.18 | Failure          |                       | Effects Analysis                           | 374        |

| 8.19 |                  | y – Look Be           |                                            | 376        |

| 8.20 |                  | •                     | Problem – Looking at the System            | 376        |

| 8.21 |                  | -                     | lem – Looking at Potential Vulnerabilities | 377        |

| 8.22 |                  |                       | Problem – Looking at the Attacks           | 378        |

|      | 8.22.1           | Looking a             | t the Software                             | 378        |

|      | 8.22.2           |                       | t the Hardware                             | 381        |

| 8.23 | Dealing          | g with the Pr         | oblem – Protecting Against the Attacks     | 382        |

|      | 8.23.1           | Protecting            | the Software                               | 382        |

|      |                  | 8.23.1.1              | First Steps                                | 382        |

|      |                  | 8.23.1.2              | Second Steps                               | 384        |

|      |                  | 8.23.1.3              | Third Steps                                | 385        |

|      |                  | 8.23.1.4              | Fourth Steps                               | 386        |

|      | 8.23.2           |                       | Testing Tools                              | 387        |

|      | 8.23.3           |                       | the Hardware                               | 388        |

|      |                  | 8.23.3.1              | First Steps                                | 388        |

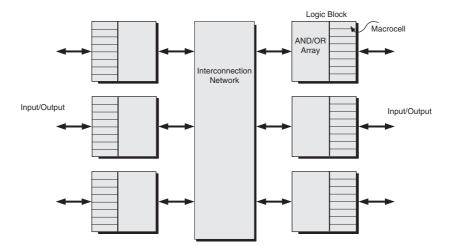

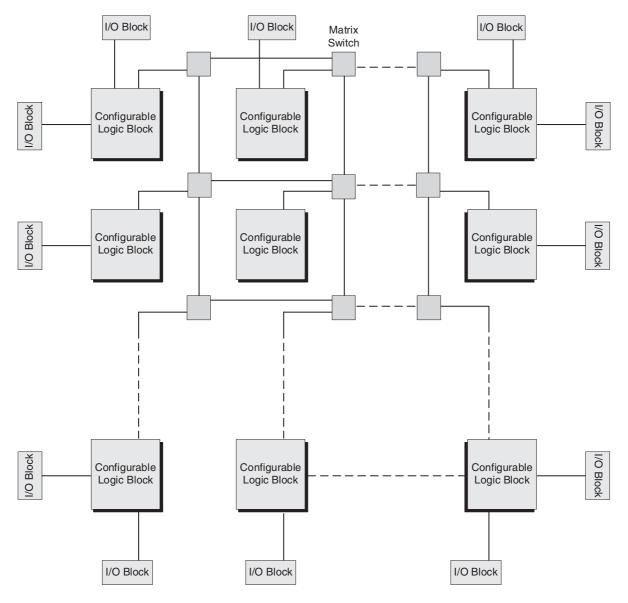

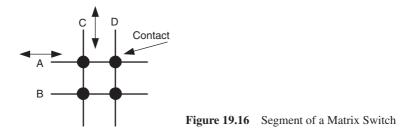

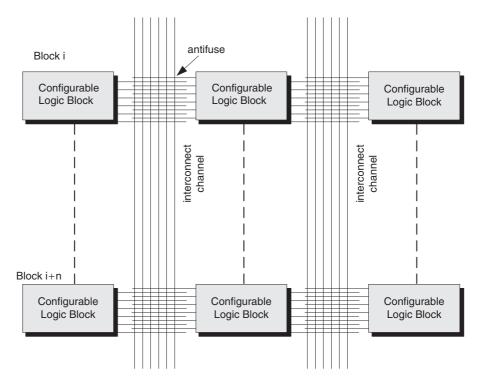

|      |                  | 8.23.3.2              | Second Steps                               | 388        |